Hi TI expert

We face MCAN RX ISR delay issue with multi CAN message in AM263x SDK V8.2

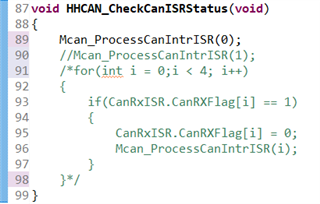

(1)When we only enable Mcan_ProcessCanIntrISR(0) for CAN0 which trigger by 1ms task

Mcan_ProcessCanIntrISR(0) trigger have delay issue(200~1000ms) when received 200ms period message

(2)CAN bus loading(~4%) as following :

CAN ID:0x228 and 0x504 for CAN0 transmit (RX shows in CAN tools)

others CAN ID for CAN0 receive (TX shows in CAN tools) ,

Have any suggestion for Mcan_ProcessCanIntrISR usage for multi CAN message?

BR

Jay