Other Parts Discussed in Thread: SYSCONFIG

Hi Team,

My customer has a question as below.

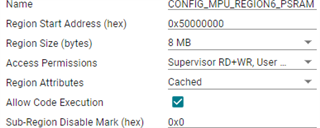

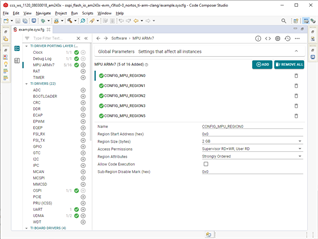

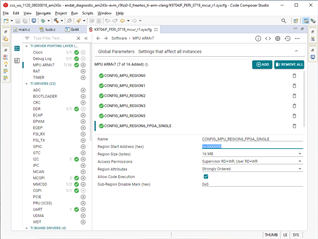

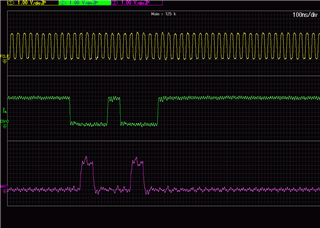

We are doing a 16-bit single read access to the FPGA with GPMC, and we observed a waveform that looks like two accesses are being made. Looking at the address, it appears that the second read is an extra read for the next address.

The GPMC setting is Multiplexed address data 16bit device. Please refer to the excel sheet below for the settings/configurations.

Does this phenomenon correspond to errata i2313?

If this errata corresponds to i2313, is it correct to say that the errata will be resolved in Rev2, but only one 16-bit access will be made?

Also, according to the errata, it is stated that incorrect data is read when 16-bit read access is performed, but specifically what kind of incorrect data is read? (Does it return the second access data? Returns a random value?)

Best regards,

Mari Tsunoda