Other Parts Discussed in Thread: HALCOGEN

Hello,

Is it possible to use mibSPI as standard SPI ? If yes, do you have code example ?

Best Regards,

Cosmin Briceag

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Cosmin,

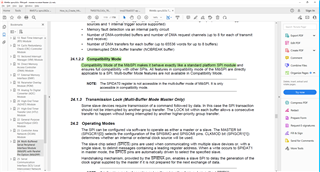

Yes, it is possible. The MibSPI will operate in two modes Compatibility and Multibuffer modes, In Compatibility mode the MibSPI exactly behaves like SPI

Can you please go through below thread

there is a code attached for LC4357 and you can take that as reference and can apply same configurations in your HALCoGen also and try.

or else

you can try below link as well

6.1. Project 0 — Hercules Safety MCUs Documentation

If you face still confusion after referring above links, then i can make you an example code for RM48x.

--

Thanks & Regards,

Jagadish.

Hi Jagadish,

Sorry for late response. Well, I managed to make it work only for SPI3. Altought the SPI1 has the same configuration, the clock is not generated. Another strange thing is that the logic analyzer records MOSI/MISO activity without the clock being generated. I used the same logic analyzer for SPI3 and everything is good there. I use my own CS.

Is there anything special I shall do for SPI1 ?

/** bring SPI out of reset */

spiREG1->GCR0 = 0U;

spiREG1->GCR0 = 1U;

/** SPI1 master mode and clock configuration */

spiREG1->GCR1 = (spiREG1->GCR1 & 0xFFFFFFFCU) | ((uint32)((uint32)1U << 1U) /* CLOKMOD */

| 1U); /* MASTER */

/** SPI1 enable pin configuration */

spiREG1->INT0 = (spiREG1->INT0 & 0xFEFFFFFFU)| (uint32)((uint32)0U << 24U); /* ENABLE HIGHZ */

/** - Delays */

spiREG1->DELAY = (uint32)((uint32)0U << 24U) /* C2TDELAY */

| (uint32)((uint32)0U << 16U) /* T2CDELAY */

| (uint32)((uint32)0U << 8U) /* T2EDELAY */

| (uint32)((uint32)0U << 0U); /* C2EDELAY */

/** - Data Format 0 */

spiREG1->FMT0 = (uint32)((uint32)0U << 24U) /* wdelay */

| (uint32)((uint32)0U << 23U) /* parity Polarity */

| (uint32)((uint32)0U << 22U) /* parity enable */

| (uint32)((uint32)0U << 21U) /* wait on enable */

| (uint32)((uint32)0U << 20U) /* shift direction */

| (uint32)((uint32)0U << 17U) /* clock polarity */

| (uint32)((uint32)0U << 16U) /* clock phase */

| (uint32)((uint32)21U << 8U) /* baudrate prescale */

| (uint32)((uint32)8U << 0U); /* data word length */

/** - Data Format 1 */

spiREG1->FMT1 = (uint32)((uint32)0U << 24U) /* wdelay */

| (uint32)((uint32)0U << 23U) /* parity Polarity */

| (uint32)((uint32)0U << 22U) /* parity enable */

| (uint32)((uint32)0U << 21U) /* wait on enable */

| (uint32)((uint32)0U << 20U) /* shift direction */

| (uint32)((uint32)0U << 17U) /* clock polarity */

| (uint32)((uint32)0U << 16U) /* clock phase */

| (uint32)((uint32)109U << 8U) /* baudrate prescale */

| (uint32)((uint32)16U << 0U); /* data word length */

/** - Data Format 2 */

spiREG1->FMT2 = (uint32)((uint32)0U << 24U) /* wdelay */

| (uint32)((uint32)0U << 23U) /* parity Polarity */

| (uint32)((uint32)0U << 22U) /* parity enable */

| (uint32)((uint32)0U << 21U) /* wait on enable */

| (uint32)((uint32)0U << 20U) /* shift direction */

| (uint32)((uint32)0U << 17U) /* clock polarity */

| (uint32)((uint32)0U << 16U) /* clock phase */

| (uint32)((uint32)109U << 8U) /* baudrate prescale */

| (uint32)((uint32)16U << 0U); /* data word length */

/** - Data Format 3 */

spiREG1->FMT3 = (uint32)((uint32)0U << 24U) /* wdelay */

| (uint32)((uint32)0U << 23U) /* parity Polarity */

| (uint32)((uint32)0U << 22U) /* parity enable */

| (uint32)((uint32)0U << 21U) /* wait on enable */

| (uint32)((uint32)0U << 20U) /* shift direction */

| (uint32)((uint32)0U << 17U) /* clock polarity */

| (uint32)((uint32)0U << 16U) /* clock phase */

| (uint32)((uint32)109U << 8U) /* baudrate prescale */

| (uint32)((uint32)16U << 0U); /* data word length */

/** - set interrupt levels */

spiREG1->LVL = (uint32)((uint32)0U << 9U) /* TXINT */

| (uint32)((uint32)0U << 8U) /* RXINT */

| (uint32)((uint32)0U << 6U) /* OVRNINT */

| (uint32)((uint32)0U << 4U) /* BITERR */

| (uint32)((uint32)0U << 3U) /* DESYNC */

| (uint32)((uint32)0U << 2U) /* PARERR */

| (uint32)((uint32)0U << 1U) /* TIMEOUT */

| (uint32)((uint32)0U << 0U); /* DLENERR */

/** - clear any pending interrupts */

spiREG1->FLG |= 0xFFFFU;

/** - enable interrupts */

spiREG1->INT0 = (spiREG1->INT0 & 0xFFFF0000U)

| (uint32)((uint32)0U << 9U) /* TXINT */

| (uint32)((uint32)0U << 8U) /* RXINT */

| (uint32)((uint32)0U << 6U) /* OVRNINT */

| (uint32)((uint32)0U << 4U) /* BITERR */

| (uint32)((uint32)0U << 3U) /* DESYNC */

| (uint32)((uint32)0U << 2U) /* PARERR */

| (uint32)((uint32)0U << 1U) /* TIMEOUT */

| (uint32)((uint32)0U << 0U); /* DLENERR */

/** @b initialize @b SPI1 @b Port */

/** - SPI1 Port output values */

spiREG1->PC3 = (uint32)((uint32)1U << 0U) /* SCS[0] */

| (uint32)((uint32)1U << 1U) /* SCS[1] */

| (uint32)((uint32)1U << 2U) /* SCS[2] */

| (uint32)((uint32)1U << 3U) /* SCS[3] */

| (uint32)((uint32)1U << 4U) /* SCS[4] */

| (uint32)((uint32)1U << 5U) /* SCS[5] */

| (uint32)((uint32)0U << 8U) /* ENA */

| (uint32)((uint32)0U << 9U) /* CLK */

| (uint32)((uint32)0U << 10U) /* SIMO[0] */

| (uint32)((uint32)0U << 11U) /* SOMI[0] */

| (uint32)((uint32)0U << 17U) /* SIMO[1] */

| (uint32)((uint32)0U << 25U); /* SOMI[1] */

/** - SPI1 Port direction */

spiREG1->PC1 = (uint32)((uint32)0U << 0U) /* SCS[0] */

| (uint32)((uint32)0U << 1U) /* SCS[1] */

| (uint32)((uint32)0U << 2U) /* SCS[2] */

| (uint32)((uint32)0U << 3U) /* SCS[3] */

| (uint32)((uint32)0U << 4U) /* SCS[4] */

| (uint32)((uint32)0U << 5U) /* SCS[5] */

| (uint32)((uint32)0U << 8U) /* ENA */

| (uint32)((uint32)1U << 9U) /* CLK */

| (uint32)((uint32)1U << 10U) /* SIMO[0] */

| (uint32)((uint32)0U << 11U) /* SOMI[0] */

| (uint32)((uint32)0U << 17U) /* SIMO[1] */

| (uint32)((uint32)0U << 25U); /* SOMI[1] */

/** - SPI1 Port open drain enable */

spiREG1->PC6 = (uint32)((uint32)0U << 0U) /* SCS[0] */

| (uint32)((uint32)0U << 1U) /* SCS[1] */

| (uint32)((uint32)0U << 2U) /* SCS[2] */

| (uint32)((uint32)0U << 3U) /* SCS[3] */

| (uint32)((uint32)0U << 4U) /* SCS[4] */

| (uint32)((uint32)0U << 5U) /* SCS[5] */

| (uint32)((uint32)0U << 8U) /* ENA */

| (uint32)((uint32)0U << 9U) /* CLK */

| (uint32)((uint32)0U << 10U) /* SIMO[0] */

| (uint32)((uint32)0U << 11U) /* SOMI[0] */

| (uint32)((uint32)0U << 17U) /* SIMO[1] */

| (uint32)((uint32)0U << 25U); /* SOMI[1] */

/** - SPI1 Port pullup / pulldown selection */

spiREG1->PC8 = (uint32)((uint32)1U << 0U) /* SCS[0] */

| (uint32)((uint32)1U << 1U) /* SCS[1] */

| (uint32)((uint32)1U << 2U) /* SCS[2] */

| (uint32)((uint32)1U << 3U) /* SCS[3] */

| (uint32)((uint32)1U << 4U) /* SCS[4] */

| (uint32)((uint32)1U << 5U) /* SCS[5] */

| (uint32)((uint32)1U << 8U) /* ENA */

| (uint32)((uint32)1U << 9U) /* CLK */

| (uint32)((uint32)1U << 10U) /* SIMO[0] */

| (uint32)((uint32)1U << 11U) /* SOMI[0] */

| (uint32)((uint32)1U << 17U) /* SIMO[1] */

| (uint32)((uint32)1U << 25U); /* SOMI[1] */

/** - SPI1 Port pullup / pulldown enable*/

spiREG1->PC7 = (uint32)((uint32)1U << 0U) /* SCS[0] */

| (uint32)((uint32)0U << 1U) /* SCS[1] */

| (uint32)((uint32)0U << 2U) /* SCS[2] */

| (uint32)((uint32)1U << 3U) /* SCS[3] */

| (uint32)((uint32)1U << 4U) /* SCS[4] */

| (uint32)((uint32)1U << 5U) /* SCS[5] */

| (uint32)((uint32)1U << 8U) /* ENA */

| (uint32)((uint32)0U << 9U) /* CLK */

| (uint32)((uint32)0U << 10U) /* SIMO[0] */

| (uint32)((uint32)1U << 11U) /* SOMI[0] */

| (uint32)((uint32)1U << 17U) /* SIMO[1] */

| (uint32)((uint32)1U << 25U); /* SOMI[1] */

/* SPI1 set all pins to functional */

spiREG1->PC0 = (uint32)((uint32)0U << 0U) /* SCS[0] */

| (uint32)((uint32)0U << 1U) /* SCS[1] */

| (uint32)((uint32)0U << 2U) /* SCS[2] */

| (uint32)((uint32)0U << 3U) /* SCS[3] */

| (uint32)((uint32)0U << 4U) /* SCS[4] */

| (uint32)((uint32)0U << 5U) /* SCS[5] */

| (uint32)((uint32)0U << 8U) /* ENA */

| (uint32)((uint32)1U << 9U) /* CLK */

| (uint32)((uint32)1U << 10U) /* SIMO[0] */

| (uint32)((uint32)1U << 11U) /* SOMI[0] */

| (uint32)((uint32)0U << 17U) /* SIMO[1] */

| (uint32)((uint32)0U << 25U); /* SOMI[1] */

/** - Initialize TX and RX data buffer Status */

g_spiPacket_t[0U].tx_data_status = SPI_READY;

g_spiPacket_t[0U].rx_data_status = SPI_READY;

/** - Finally start SPI1 */

spiREG1->GCR1 = (spiREG1->GCR1 & 0xFEFFFFFFU) | 0x01000000U;Hi Cosmin,

I don't know which board you are using, and on which pins of SPI1 you are measuring the signal.

If possible, try to attach entire your project so that i can verify your pin configurations and initializations.

Or else please make sure below things,

1. Make sure to enable MibSPI1 in pinmux configurations

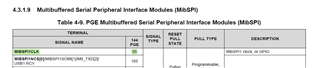

2. If you are using PGE package then MIBSPI1CLK is on 95th pin of the device, so make sure you are taping the right pin on your board

--

Thanks & Regards,

Jagadish.