Other Parts Discussed in Thread: HALCOGEN

Hi BU experts,

My customer found 7 pcs TMS570LS0432-based board have no CAN output under low temperature (-40 °C). They did low temperature test on the failure board and I supported them on-site.

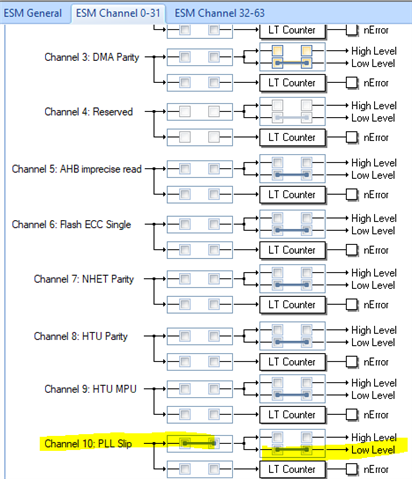

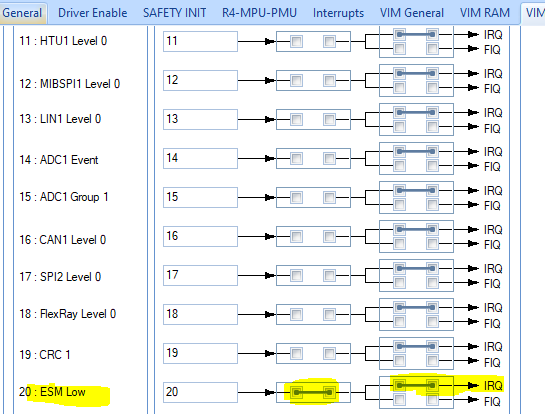

Under -40 °C ambient temperature, configured the CAN working in External Loopback mode and monitored the CAN TX line. We found that actually there are data in TX line but the baud rate is not right (only 125 kbps but the expected is 500 kbps). This phenomenon indicates that the clock of CAN controller is not right. So we checked the crystal oscillator and the PLL status. The crystal oscillator is fine, but we found that GLBSTAT.RFSLIP bit is set which means that "A PLL under cycle slip has been detected".

My customer wants to know:

1). why "PLL under cycle slip" is happened and what is the probability of this phenomenon?

2). It seems that this failure is related to temperature and is a transient failure, does Errata Note include this one? ( I checked Errata notes of Silicon Rev A, I would like to check with you if this failure is similar to SSWF021#45?

3). Does TI have workaround to detect this failure under normal temperature or low temperature? And workarounds to avoid it?

4). They also want to do Failure Analysis, do we support do this low temperature FA?

Thanks. This failure has caused a relatively serious impact on the customer side, please help check this asap.

BR,

Will