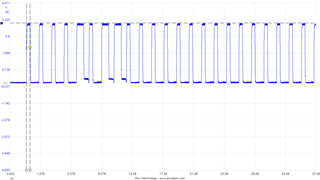

I am attempting to use SPI to drive a string of of ws2812b neopixels. I am using an array of bytes to create the bit pattern that I want to send out to the LEDs, this is almost working, except that when I send my array of bytes out i can see (using a scope) that there is a delay of 710ns between each byte that is transmitted. Is there any way to reduce, or better still, eliminate this delay ?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.