Part Number: MSP432E411Y-BGAEVM

Dear Team,

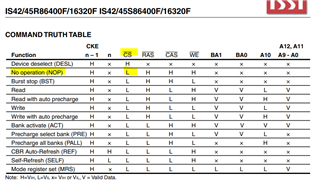

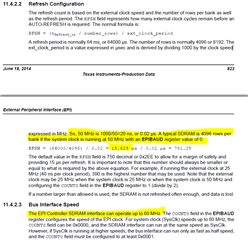

in our custom design of MSP432E401Y SDRAM is connected with EPI Bus interface. But there is single pin change when compared with given SDRAM example code of SDK.

The change are as follows:

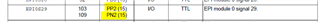

1.Example code as following GPIO for EPIOS0

ROM_GPIOPinConfigure(GPIO_PH0_EPI0S0);

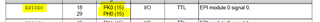

2.Our custom design contains GPIO for EPIOS0

the changes i made as follows:

ROM_GPIOPinConfigure(GPIO_PK0_EPI0S0);

MAP_GPIOPinTypeEPI(GPIO_PORTK_BASE, (GPIO_PIN_5|GPIO_PIN_0));

3. What are changes need to done to make SDRAM work.

Regards,

Naga Narasimha Rao