Hi,

To my understanding, High-end ARM processors based on Cortex-A and Cortex-R include Performance Monitor Unit (PMU) which provides information like cycle counts.

Is there a way to activate this performance counter on the TI RM46?

Reference: ARM Cortex-R4 reference

Following this application note : https://www.ti.com/lit/fs/spna138a/spna138a.pdf?ts=1675176362803

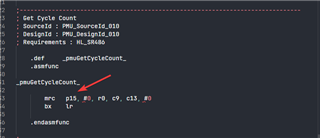

I get the following

_pmuInit_(); _pmuEnableCountersGlobal_(); _pmuSetCountEvent_(pmuCOUNTER0, PMU_CYCLE_COUNT); // PMU_INST_ARCH_EXECUTED _pmuResetCounters_(); _pmuStartCounters_(pmuCOUNTER0); cycles_PMU_start = _pmuGetEventCount_(pmuCOUNTER0); code_to_be_measured(); _pmuStopCounters_(pmuCOUNTER0); cycles_PMU_end = _pmuGetEventCount_(pmuCOUNTER0); cycles_PMU_measure = cycles_PMU_end - cycles_PMU_start;

That said, it doesn't appear to work when I put this code in sys_main.c: the cycles_PMU_measure is still at 0.

Any help is appreciated.

Best,

Gabriel