Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi Team

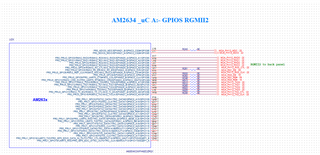

I have been using CPSW with a single MDIO interface (MDIO0_MDC/MDIO) to enable two RGMII ports. Currently, CPSW RGMII1 is configured to use the MDIO0_MDC/MDIO pins, while PRU0 ICSSM RGMII is configured to use the PR0_MDIO0_MDC/MDIO pins. My understanding is that I have correctly enabled CPSW RGMII1 through CPSW and the PRU0 ICSSM RGMII through ICSSM. Could you please confirm if this setup is valid?

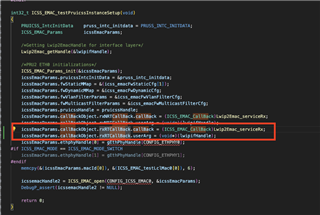

What are the required steps to initialize PRU0 ICSSM Ethernet with RGMII support in the MCU+ SDK?

What is the correct way to configure PRU0 ICSSM RGMII and PR0_MDIO0 in SysConfig for Ethernet?

Are there any pinmux constraints or conflicts when using ICSSM alongside CPSW, especially with overlapping RGMII/MDIO pins?

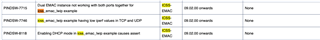

Can ICSSM and CPSW MDIO interfaces operate independently without conflict? How does the SDK handle dual MDIO domains (MDIO0 and PR0_MDIO0)?

Are there any configuration options or APIs to select between dual-MAC and switch mode for ICSSM Ethernet in SDK 10.00.00.35?

Please help me resolving the issue.

Thanks in advance.