Hi,

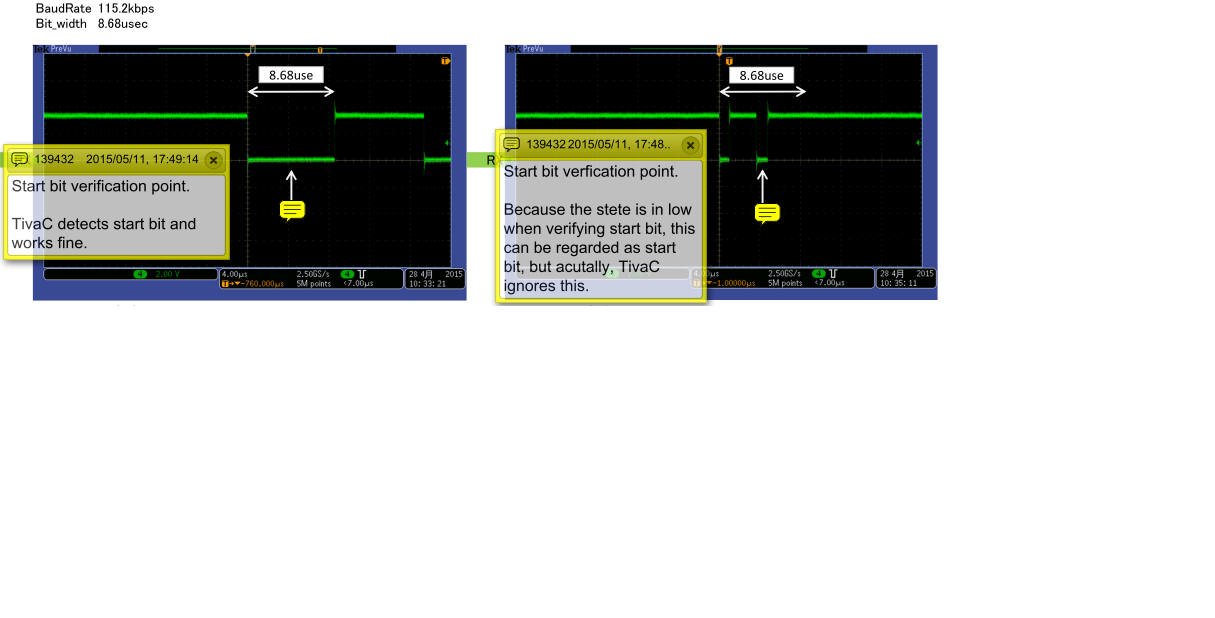

My customer needs to clarify UART start bit verification.

Datasheet (TM4C123x) says that:

The start bit is valid and recognized if the UnRx signal is still low on the eighth cycle of Baud16 (HSE clear) or the fourth cycle of Baud 8 (HSE set), otherwise it is ignored. After a valid start bit is detected, successive data bits are sampled on every 16th cycle of Baud16 or 8th cycle of Baud8 (that is, one bit period later) according to the programmed length of the data characters and value of the HSE bit in UARTCTL. The parity bit is then checked if parity mode is enabled. Data length and parity are defined in the UARTLCRH register.

Now let's assume we are using Baud16 for UART. In this case, the above descriptions lead us to understand the start bit is validated by *only* 8th clock of Baud16.

Is this correct ? Can I assume that 2nd and 3rd (...and so forth, upto 7th) clocks of Baud16 are never used to verify the start bit ?

Best Regards,

Kawada