Greetings,

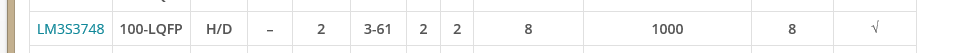

I'm modifying a legacy software application with an LM3S3748 Stellaris processor. There was an issue with tool archival and only the 'source' directory has been preserved. Tools and other directories are gone.

I've installed the latest version of Code Composer Studio (6.1.1.00022; compiler 5.2.5, 5.1.14, 15.12.2 ), along with SW-DRL-10636 and SW-USBL-10636. The 'SW' packages have resolved the missing dependencies (at least what I see for the moment).

The issue I'm wrestling with is apparently the pin definitions have changed. There is now a pin_map.h that is also used with hw_gpio.h. This is fine, however specific definitions are not present.

Example:

GPIO_PA5_SSI0TX - MISSING

However, the below are present

#define SSI0TX_PERIPH SYSCTL_PERIPH_GPIOA

#define SSI0TX_PORT GPIO_PORTA_BASE

#define SSI0TX_PIN GPIO_PIN_5

Does anyone know where to find the original 'h' file that contained the definitions?

Curiously, the definitions are available for other parts, but not the LM3S3748 (ex.LM3S9G97)

Alternatively, suggestions on modification of the pins to match the definitions? Certainly reading the datasheet and reviewing the schematic, I can manually set these up, but I'm hoping to limit the regression testing needed (still have not made the required changes yet).

Missing items:

identifier "GPIO_PE3_SSI1TX" is undefined

identifier "GPIO_PE2_SSI1RX" is undefined

identifier "GPIO_PE1_SSI1FSS" is undefined

identifier "GPIO_PE0_SSI1CLK" is undefined

identifier "GPIO_PA5_SSI0TX" is undefined

identifier "GPIO_PA4_SSI0RX" is undefined

identifier "GPIO_PA3_SSI0FSS" is undefined

identifier "GPIO_PA2_SSI0CLK" is undefined

Any assistance would be greatly appreciated.

Regards

JMA