Picture.xlsx1. customer issue describe

Here is one issue that customer found when another MCU use I2C master write read with repeated start condition to TI chip.

The test program in TI chip only initialize GPIO pin 2, 3 as I2C function and act as slave.

The interrupt handler is very simple.

I2C handler read all master request package data when interrupt rise I2C_SLAVE_ACT_RREQ_FBR and I2C_SLAVE_ACT_RREQ status flag without any process action.

- Only “i2cDate = I2CSlaveDataGet(I2C0_SLAVE_BASE)”

And write back 0xF0 constant value when interrupt rise I2C_SLAVE_ACT_TREQ status flag. (depend on master read number)

- I2CSlaveDataPut(I2C0_SLAVE_BASE, 0xF0);

From the TI driverlib “TivaWare_C_Series-2.1.3.156” seems it direct write to I2CSDR register in hardware I2C controller.

But, the actually result measure from oscilloscope seems always fail in first four bytes value after response slave address to master.

And they also didn’t see any explain about slave read after repeated start condition in “Datasheet”.

Interrupt handler:

Customer did a simple test: after repeated start, slave always write 0xF0

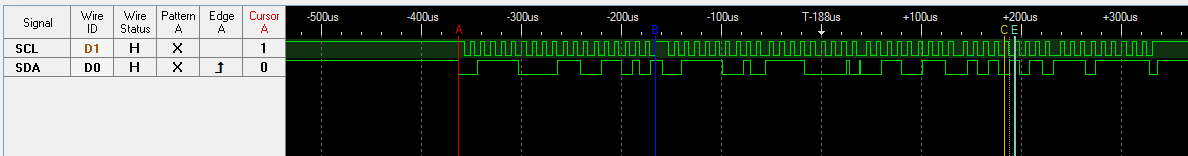

The test waveform is Fig1 and Fig2(Fig2 is a continuation of Fig1)

Red(marked 1) – response slave address

Orange(marked 2) – slave write 0xF0(sometimes will be error)

Purple(marked 3,4,5) – slave write 0x00(should be 0xF0, they are error)

Green(marked 6,7) – slave write 0xF0(they are right, from marked 6, slave write will always right)

Fig1

Fig2

Please find the picture as attached. thanks!

2. Support need:

Master->Slave(TI TM4C123), please help to do the test with the below sequence

-

Master write to slave

-

repeat start read data from slave

-

read byte >5 byte

if all read byte is correct, please kindly provide your code to us, and I will ask customer do the test with your code.

If you can emersion the customer issue, please kindly give your comment.

Thanks a lot!