TM4C1294NCPDTi3 and older LM3S8971 MCU had similar issue though not understood why motor phase current was randomly bursting years ago.

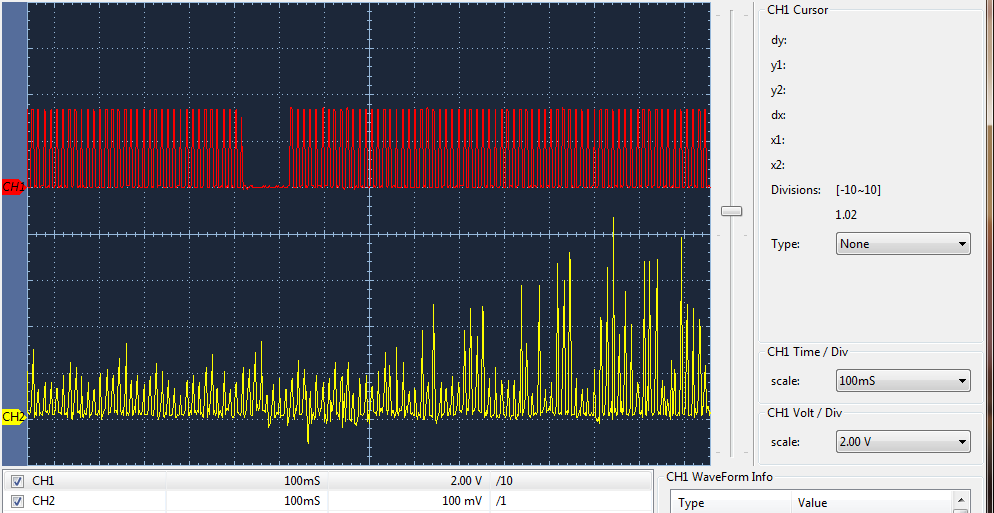

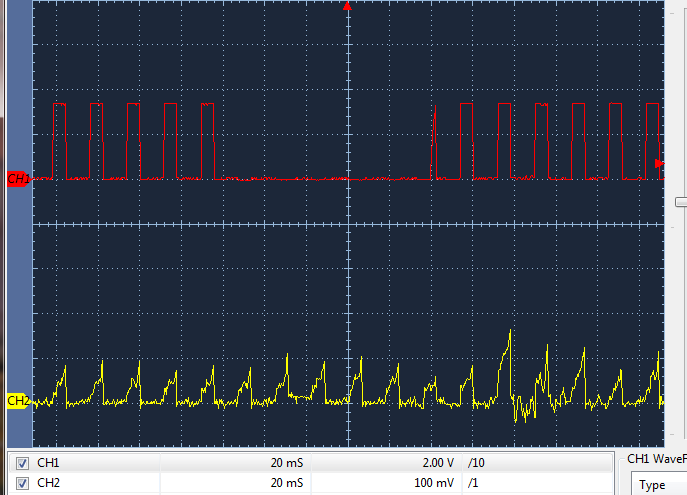

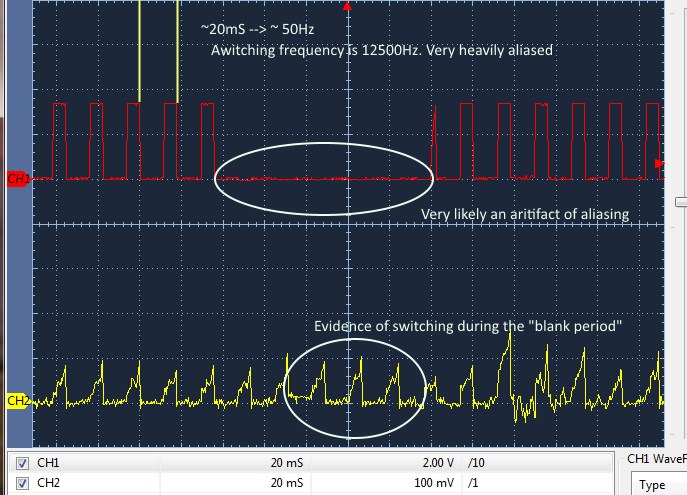

3 PWM generators (GEN_MODE_SYNC) will suddenly stop or perhaps only PWM control block outputs Null for 150-275ms (CH1). The result is all 3 phase currents CH2 randomly burst to catch up to the current lag. Have noticed this current burst LM3S8971 MCU and thought it was normal inverter noise.

Motor commutation just stops then picks back up where it left off. FOC use GPTM-0 (one shot mode) to trigger PWM control block pin state changes from ADC samples of BEMF motor phases crossing zero to commutate 3 phases. Nulls occur on all 6 PWM control block outputs in some order that does not stall a running motor yet disrupts current in a bad way. The more time spent to examine older motorware the more things discover that were not so obvious at first.

What could be causing 150ms nulls on the PWM output control block configured local updates? Note ADC sequencer (BEMF sample) holds highest priority over all sequencers, same is true for GPTM-0?

A few microseconds is acceptable Null time; 150ms = 1875 PWM pulses at 12.5Khz are randomly missing.

Note scope rolling 500ms 100ms/cm and 20 seconds of PWM pulses (CH1) occurs prior to Null and phase burst current follows (CH2 trigger source).

2.15.2017: PWM void was caused by a bad MCU where VDD measured 240 ohms to ground and 0.2v drop on diode check.

https://e2e.ti.com/support/microcontrollers/tiva_arm/f/908/p/580563/2133645#2133645