Hi, I have an urgent matter with TM4C123BE6PZ!

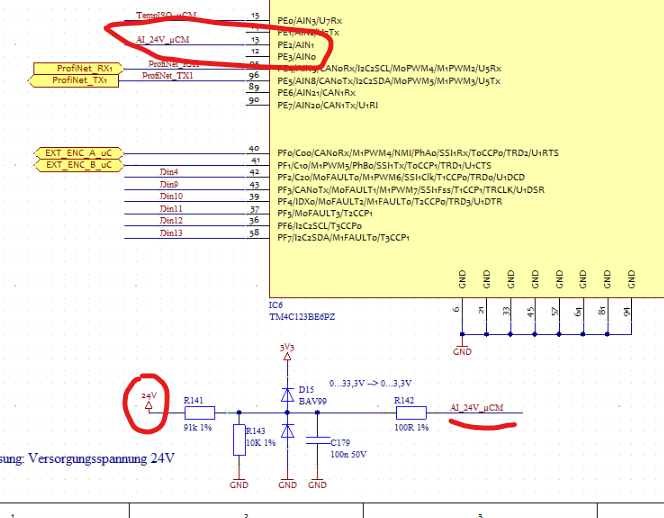

Our customer uses the analog input AIN2/PE2 to measure the 24V supply voltage of the whole board.

The 24V is divided with a 91K/10k voltage divider and protected with a 100n ceramic cap, a clamping Diode and a series 100R resistor in front of the pin.

See partial block diagram attached.

The problem they have, is that when they turn on the main supply (24V) in some cases (maybe 1 of 50) the controller dies for any reason.

When they remove the 91k and no 24V are on the divider, then no failure happens!

Are there any known issues with this Port Pin?

Have you any guess what could be the problem?

Regards,

Jon