Other Parts Discussed in Thread: TIDA-00778, LM3S8971, UCC27714, LM94022, , TMS320F28027

Hello group,

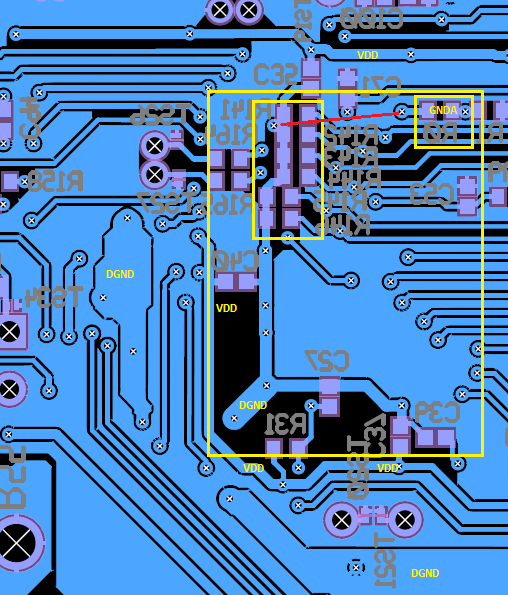

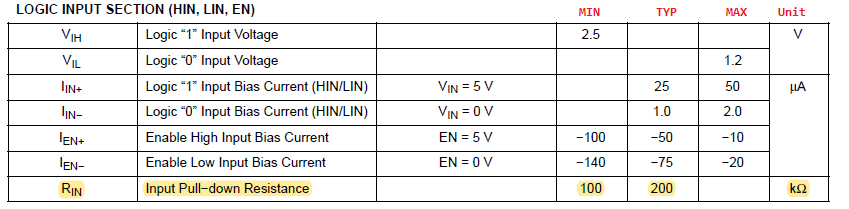

I have been pondering ramifications ADC SNR by 20K pull downs near the MCU pins tied to digital ground, 6 PWM outputs. The PWM output traces lead to analog driver 100k internal pull downs 2" away. The parallel resistances 20K reduces 100k internal input pull downs to roughly 16k overall. Seemingly this practice of adding 10-20k pull downs to analog gate drivers is a breading ground for high frequency PWM riding on ground.

How does that impact SNR of ADC samples and stability? It seems TI engineers TIDA-00778 added 10K pull downs likely for reason POR pin float, any guesses? Typically gate drivers have 100-200k internal pull downs on the inputs so why add any parallel resistance and dampen GPIO current slew? Has there been any study by TI to show how PWM signal injection to MCU ground can or will lead to ADC issues?

Roughly 167µV of current dumped to digital ground x 6 GPIO pins or 1.002mA every 50µs at 20Khz. Do GPIO pins glitch during POR or change state if low impedance resistance is not placed directly near the MCU package pins?

Perhaps one plausible reason for adding any parallel resistor pull downs was to lower the trace impedance if GPIO glitching should randomly occur? This same practice of adding 20k pull downs to GPIO was present on the LM3S8971 motor RDK but only on the low side near the gate driver input also having internal 400k pull downs.