Hi,

My customer is developing a 3 phase full bridge inverter. He wants to change the frequency of each phase.

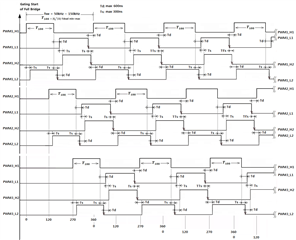

The waveform below is what he want to implement.

I have attached source code of PWM configuration.

It consists of EPWM1(Master) / EPWM2~EPMW6(Slave) and set the 3-phase PWM waveform to have a phase of 120 degrees as shown in above pictures

Three-phase consists of PWM1/2, 3/4 and 5/6 pairs.

void BSW_SET_Freq ( byte u8_ch, single f32_freq )

{

ePWM_Regs[ u8_ch ]->TBPRD = ( word ) ( ( single ) CPU_SPD / ( f32_freq * 2.0f ) - 1.0F );

}

void BSW_SET_Duty ( byte u8_ch, single f32_duty )

{

ePWM_Regs[ u8_ch ]->CMPA.bit.CMPA = ( word )( ( single )ePWM_Regs[ u8_ch ]->TBPRD * f32_duty );

ePWM_Regs[ u8_ch ]->CMPB.bit.CMPB = ( word )( ( single )ePWM_Regs[ u8_ch ]->TBPRD * f32_duty );

}

void BSW_updatePhase ( byte ch, single phase, byte LayerOn )

{

word phaseCount=0;

single DEGREE_SCALE;

DEGREE_SCALE = 1.0f/180.0f;

if(LayerOn == EN_CAN_On)

{

if( phase < 0.0f )

{

ePWM_Regs[ ch ]->TBCTL.bit.PHSDIR = 1;

phaseCount = ( word ) ( ( single ) ePWM_Regs[ ch ]->TBPRD * -phase * DEGREE_SCALE );

}

else

{

ePWM_Regs[ ch ]->TBCTL.bit.PHSDIR = 0;

phaseCount = ( word ) ( ( single ) ePWM_Regs[ ch ]->TBPRD * phase * DEGREE_SCALE );

}

if (( ch == 1 ) || ( ch == 3 ) || ( ch == 6 ))

{

ePWM_Regs[ ch ]->TBPHS.bit.TBPHS = phaseCount;

}

else

{

ePWM_Regs[ ch ]->TBPHS.bit.TBPHS = phaseCount+LLC_ShiftTIME;

}

}

else

{

ePWM_Regs[ ch ]->TBPHS.bit.TBPHS = 0;

}

}

//EPWM1 Master 설정

void InitEPwm1Example ( void )

{

//

// Setup TBCLK

//

EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE;

EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO;

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count up

EPwm1Regs.TBPRD = EPWM1_TIMER_TBPRD; // Set timer period

EPwm1Regs.TBPHS.bit.TBPHS = 0x0000; // Phase is 0

EPwm1Regs.TBCTR = 0x0000; // Clear counter

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm1Regs.TBCTL.bit.PRDLD = TB_SHADOW;

//

// Setup shadow register load on ZERO

//

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

//

// Set Compare values

//

EPwm1Regs.CMPA.bit.CMPA = EPWM1_MIN_CMPA; // Set compare A value

EPwm1Regs.CMPB.bit.CMPB = EPWM1_MAX_CMPB; // Set Compare B value

//

// Set actions

//

EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR; // Set PWM1A on Zero

EPwm1Regs.AQCTLA.bit.CAD = AQ_SET;

EPwm1Regs.AQCTLB.bit.CAU = AQ_CLEAR; // Set PWM1A on Zero

EPwm1Regs.AQCTLB.bit.CAD = AQ_SET;

EPwm1Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE;

EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

EPwm1Regs.DBCTL.bit.IN_MODE = DBA_RED_DBB_FED;

BSW_SET_Deadtime(1, LLC_DEADTIME);

//

// Interrupt where we will change the Compare Values

//

EPwm1Regs.ETSEL.bit.SOCAEN = 1; /* Enable SOC on B group */

EPwm1Regs.ETSEL.bit.SOCASEL = ET_CTR_ZERO;

EPwm1Regs.ETPS.bit.SOCAPRD = ET_1ST;

}

//EPWM2 Slave 설정

void InitEPwm2Example ( void )

{

EPwm2Regs.TBCTL.bit.PHSEN = TB_ENABLE;

EPwm2Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN; //20210427 ygson modified, TB_SYNC_IN --> TB_CTR_ZERO

EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count up

EPwm2Regs.TBPRD = EPWM2_TIMER_TBPRD; // Set timer period

EPwm2Regs.TBPHS.bit.TBPHS = 60; // Phase is 0

EPwm2Regs.TBCTR = 0x0000; // Clear counter

EPwm2Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm2Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm2Regs.TBCTL.bit.PRDLD = TB_SHADOW;

//

// Setup shadow register load on ZERO

//

EPwm2Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm2Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm2Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm2Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

//

// Set Compare values

//

EPwm2Regs.CMPA.bit.CMPA = EPWM2_MIN_CMPA; // Set compare A value

EPwm2Regs.CMPB.bit.CMPB = EPWM2_MAX_CMPB; // Set Compare B value

//

// Set Actions

//

EPwm2Regs.AQCTLA.bit.CAU = AQ_SET; // Set PWM1A on Zero

EPwm2Regs.AQCTLA.bit.CAD = AQ_CLEAR;

EPwm2Regs.AQCTLB.bit.CAU = AQ_SET; // Set PWM1A on Zero

EPwm2Regs.AQCTLB.bit.CAD = AQ_CLEAR;

EPwm2Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE;

EPwm2Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

EPwm2Regs.DBCTL.bit.IN_MODE = DBA_RED_DBB_FED;

BSW_SET_Deadtime(2, LLC_DEADTIME);

//

// Interrupt where we will change the Compare Values

//

EPwm2Regs.ETSEL.bit.SOCAEN = 1; /* Enable SOC on B group */

EPwm2Regs.ETSEL.bit.SOCASEL = ET_CTR_ZERO;

EPwm2Regs.ETPS.bit.SOCAPRD = ET_1ST;

}

//EPWM3 Slave 설정

void InitEPwm3Example ( void )

{

//

// Setup TBCLK

//

EPwm3Regs.TBCTL.bit.PHSEN = TB_ENABLE;

EPwm3Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN;

EPwm3Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count up

EPwm3Regs.TBPRD = EPWM3_TIMER_TBPRD; // Set timer period

EPwm3Regs.TBPHS.bit.TBPHS = 0x0000; // Phase is 0

EPwm3Regs.TBCTR = 0x0000; // Clear counter

EPwm3Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm3Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm3Regs.TBCTL.bit.PRDLD = TB_SHADOW;

//

// Setup shadow register load on ZERO

//

EPwm3Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm3Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm3Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm3Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

//

// Set Compare values

//

EPwm3Regs.CMPA.bit.CMPA = EPWM3_MIN_CMPA; // Set compare A value

EPwm3Regs.CMPB.bit.CMPB = EPWM3_MAX_CMPB; // Set Compare B value

//

// Set actions

//

EPwm3Regs.AQCTLA.bit.CAU = AQ_CLEAR; // Set PWM1A on Zero

EPwm3Regs.AQCTLA.bit.CAD = AQ_SET;

EPwm3Regs.AQCTLB.bit.CAU = AQ_CLEAR; // Set PWM1A on Zero

EPwm3Regs.AQCTLB.bit.CAD = AQ_SET;

EPwm3Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE;

EPwm3Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

EPwm3Regs.DBCTL.bit.IN_MODE = DBA_RED_DBB_FED;

BSW_SET_Deadtime(3, LLC_DEADTIME);

//

// Interrupt where we will change the Compare Values

//

EPwm3Regs.ETSEL.bit.SOCAEN = 1; /* Enable SOC on B group */

EPwm3Regs.ETSEL.bit.SOCASEL = ET_CTR_ZERO;

EPwm3Regs.ETPS.bit.SOCAPRD = ET_1ST;

}

//EPWM4 Slave 설정

void InitEPwm4Example ( void )

{

EPwm4Regs.TBCTL.bit.PHSEN = TB_ENABLE;

EPwm4Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN; //20210427 ygson modified, TB_SYNC_IN --> TB_CTR_ZERO

EPwm4Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count up

EPwm4Regs.TBPRD = EPWM4_TIMER_TBPRD; // Set timer period

EPwm4Regs.TBPHS.bit.TBPHS = 60; // Phase is 0

EPwm4Regs.TBCTR = 0x0000; // Clear counter

EPwm4Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm4Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm4Regs.TBCTL.bit.PRDLD = TB_SHADOW;

//

// Setup shadow register load on ZERO

//

EPwm4Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm4Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm4Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm4Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

//

// Set Compare values

//

EPwm4Regs.CMPA.bit.CMPA = EPWM4_MIN_CMPA; // Set compare A value

EPwm4Regs.CMPB.bit.CMPB = EPWM4_MAX_CMPB; // Set Compare B value

//

// Set Actions

//

EPwm4Regs.AQCTLA.bit.CAU = AQ_SET; // Set PWM1A on Zero

EPwm4Regs.AQCTLA.bit.CAD = AQ_CLEAR;

EPwm4Regs.AQCTLB.bit.CAU = AQ_SET; // Set PWM1A on Zero

EPwm4Regs.AQCTLB.bit.CAD = AQ_CLEAR;

EPwm4Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE;

EPwm4Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

EPwm4Regs.DBCTL.bit.IN_MODE = DBA_RED_DBB_FED;

BSW_SET_Deadtime(4, LLC_DEADTIME);

//

// Interrupt where we will change the Compare Values

//

EPwm4Regs.ETSEL.bit.SOCAEN = 1; /* Enable SOC on B group */

EPwm4Regs.ETSEL.bit.SOCASEL = ET_CTR_ZERO;

EPwm4Regs.ETPS.bit.SOCAPRD = ET_1ST;

}

//EPWM5 Slave 설정

void InitEPwm5Example ( void )

{

//

// Setup TBCLK

//

EPwm5Regs.TBCTL.bit.PHSEN = TB_ENABLE;

EPwm5Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN;

EPwm5Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count up

EPwm5Regs.TBPRD = EPWM5_TIMER_TBPRD; // Set timer period

EPwm5Regs.TBPHS.bit.TBPHS = 60; // Phase is 0

EPwm5Regs.TBCTR = 0x0000; // Clear counter

EPwm5Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm5Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm5Regs.TBCTL.bit.PRDLD = TB_SHADOW;

//

// Setup shadow register load on ZERO

//

EPwm5Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm5Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm5Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm5Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

//

// Set Compare values

//

EPwm5Regs.CMPA.bit.CMPA = EPWM5_MIN_CMPA; // Set compare A value

EPwm5Regs.CMPB.bit.CMPB = EPWM5_MAX_CMPB; // Set Compare B value

//

// Set Actions

//

EPwm5Regs.AQCTLA.bit.CAU = AQ_SET; // Set PWM1A on Zero

EPwm5Regs.AQCTLA.bit.CAD = AQ_CLEAR;

EPwm5Regs.AQCTLB.bit.CAU = AQ_SET; // Set PWM1A on Zero

EPwm5Regs.AQCTLB.bit.CAD = AQ_CLEAR;

EPwm5Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE;

EPwm5Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

EPwm5Regs.DBCTL.bit.IN_MODE = DBA_RED_DBB_FED;

BSW_SET_Deadtime(5, LLC_DEADTIME);

//

// Interrupt where we will change the Compare Values

//

EPwm5Regs.ETSEL.bit.SOCAEN = 1; /* Enable SOC on B group */

EPwm5Regs.ETSEL.bit.SOCASEL = ET_CTR_ZERO;

EPwm5Regs.ETPS.bit.SOCAPRD = ET_1ST;

}

//EPWM6 Slave 설정

void InitEPwm6Example ( void )

{

//

// Setup TBCLK

//

EPwm6Regs.TBCTL.bit.PHSEN = TB_ENABLE;

EPwm6Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN;

EPwm6Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count up

EPwm6Regs.TBPRD = EPWM6_TIMER_TBPRD; // Set timer period

EPwm6Regs.TBPHS.bit.TBPHS = 0x0000; // Phase is 0

EPwm6Regs.TBCTR = 0x0000; // Clear counter

EPwm6Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm6Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm6Regs.TBCTL.bit.PRDLD = TB_SHADOW;

//

// Setup shadow register load on ZERO

//

EPwm6Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm6Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm6Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm6Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

//

// Set Compare values

//

EPwm6Regs.CMPA.bit.CMPA = EPWM6_MIN_CMPA; // Set compare A value

EPwm6Regs.CMPB.bit.CMPB = EPWM6_MAX_CMPB; // Set Compare B value

//

// Set Actions

//

EPwm6Regs.AQCTLA.bit.CAU = AQ_CLEAR; // Set PWM1A on Zero

EPwm6Regs.AQCTLA.bit.CAD = AQ_SET;

EPwm6Regs.AQCTLB.bit.CAU = AQ_CLEAR; // Set PWM1A on Zero

EPwm6Regs.AQCTLB.bit.CAD = AQ_SET;

EPwm6Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE;

EPwm6Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

EPwm6Regs.DBCTL.bit.IN_MODE = DBA_RED_DBB_FED;

BSW_SET_Deadtime(6, LLC_DEADTIME);

//

// Interrupt where we will change the Compare Values

//

EPwm6Regs.ETSEL.bit.SOCAEN = 1; /* Enable SOC on B group */

EPwm6Regs.ETSEL.bit.SOCASEL = ET_CTR_ZERO;

EPwm6Regs.ETPS.bit.SOCAPRD = ET_1ST;

}

When slave frequency is changed to be smaller than the master, PWM is not output.

Could I get any advice on this problem?

And could I get some examples related to 3phase full bridge inverter?