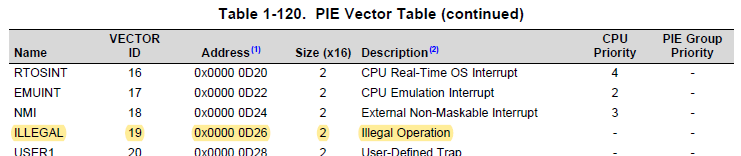

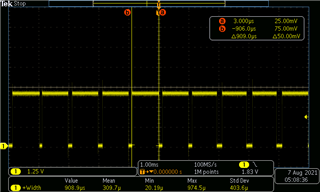

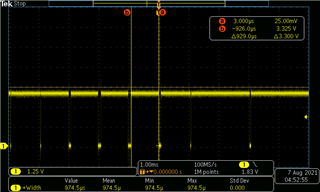

We have the aggressive interrupt timing in the project. The ADCINT1 and ADCINT2 both has the sampling rate 10us. The counter phase of ADCINT2 is set to 5us which is half of the period 10us. They are pointed to the same interrupt routine. Therefore, the interrupt rate is 5us for both ADCINT1 and ADCINT2. Also, there are other interrupt source such as HRCAP4_INT.

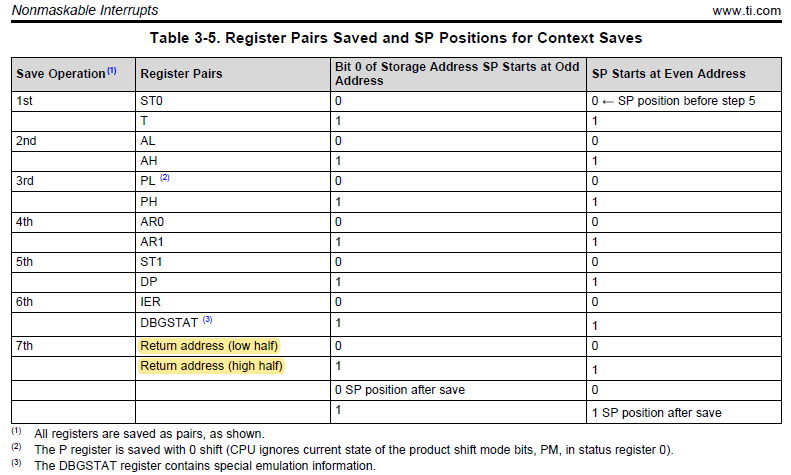

The project is built with compiler v6.1.3 without problem and working good. However, the processor halt and the code jump into the TINT0_ISR() when building with compiler TIv20.2.4.LTS.

The following is the question I submitted before and I am still having this issue.