Hello,

We are having some issues with the "Input qualifier" feature of the GPIO module. The microcontroller is receiving a bad signal (pulse) after the input qualifier is configured. This, for example, makes the MCU trigger an interrupt.

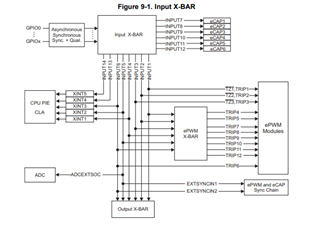

We confirmed that a fake signal transition is generated after activating the input qualifier. We configure a XBAR from that input to another pìn (assuming that the XBAR input is connected after the input qualifier). We see a pulse at the output of the XBAR, but it does not correspond with the value that we input to the pin.

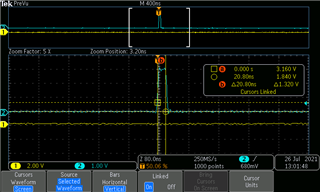

The next image shows the issue, the yellow signal is the real input value (input pin of the MCU), and the blue signal is the output of the XBAR. The blue signal has a

This is specially problematic with the "encoder index input" of the eQEP peripheral. When we configure the glitch filter to be active (qualification with 3 samples), a index pulse is received. But in this case, the eQEP module does not trigger the index event ISR automatically, it waits until A or B transition is received (we use QEPCTL[IEL] = 3). Due to that we cannot filter that interrupt on an easy way.

Is this a known issue? Could you give me a workaround to bypass the issue?

Thank you and regards,

Rodrigo.