Dear team:

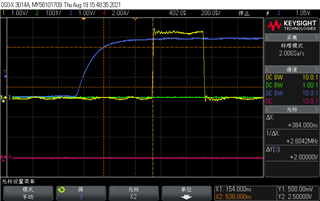

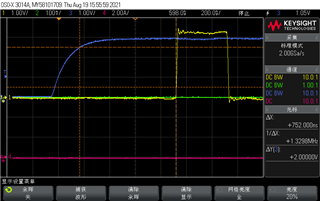

When my customer uses 28033 to implement external input triggering XINT1 interrupt (rising edge trigger, other interrupts allow the interrupt to nest), under the condition of the external input signal unchanged, it is found that the delay of entering the interrupt has a maximum of about 300 ns Difference, I don’t know if this time level difference is normal?

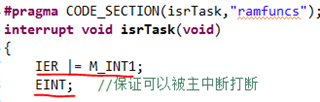

He configured a total of 3 interrupts, XINT1 interrupt priority is the highest, and other interrupts allow XINT1 nesting. In the XINT1 interrupt service routine, set GPIO high when entering the interrupt, and pull GPIO low when going out of the interrupt. The following is part of the code:

The following is a comparison chart of entering the interruption time:

Best regards