Hello!

I am use free modbus on DSP F28335.

There are critical interrupts in the DSP project that do not want to be interrupted( ADC ISR), what should I do with

"#define ENTER_CRITICAL_SECTION( ) "

"#define EXIT_CRITICAL_SECTION( ) "

Thanks!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello!

I am use free modbus on DSP F28335.

There are critical interrupts in the DSP project that do not want to be interrupted( ADC ISR), what should I do with

"#define ENTER_CRITICAL_SECTION( ) "

"#define EXIT_CRITICAL_SECTION( ) "

Thanks!

By default interrupts are disabled when you enter an ISR on C28x, so unless you are intentionally taking some action in the ISR to reenable interrupts, you shouldn't need to worry about unwanted interrupt nesting.

Are you asking how you should define those critical section macros? I expect you could just use EINT and DINT if you're just looking to globally enable/disable interrupts.

Whitney

Actually , If I define ENTER_CRITICAL_SECTION( ) DINT, DSP will cost several hundred us to deal with sci communication.

The ADC interrupt that should be executed every 50us is forced to postpone, and the PWM update executed in the ADC interrupt may brings some security risks. So if I don’t want this hidden danger, and I don’t want the ADC interrupt to be interrupted, what should I do?

By the way,I have one question that puzzled me for a long time , about EPWM:

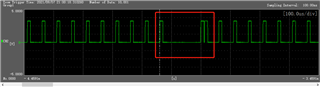

As shown above, high level means ADC ISR, if I update PWM register value Every cycle in this ADC ISR, and I use PWM compare shadow register, C code is like this:

interrupt void ADCISR(void)

{

....

EPwm1Regs.CMPA.half.CMPA = a1;

EPwm4Regs.CMPA.half.CMPA = a2;

EPwm2Regs.CMPA.half.CMPA = b1; //<------------------------

EPwm5Regs.CMPA.half.CMPA = b2;

EPwm3Regs.CMPA.half.CMPA = c1;

EPwm6Regs.CMPA.half.CMPA = c2;

...

}

Is there such a possibility: when DSP Finished "EPwm2Regs.CMPA.half.CMPA = b1;" , PWM transfers the values of all shadow registers to the PWM action registers, which causes the value of "EPwm2Regs.CMPA.half.CMPA" to be the result of a new cycle calculation, while the value of "EPwm5Regs.CMPA.half.CMPA" is still the previous cycle result of the calculation. If these two PWMs control the upper and lower tubes of the same bridge , is there a possibility that the upper and lower bridge are directly connected?

As I said, ISRs will not be interrupted by default on the C28x unless you put code in the ISR to reenable interrupts. Perhaps what you mean is that the execution of the ADC ISR is being delayed by the ENTER_CRITICAL_SECTION()?

If you want the ADC ISR to be exempt from ENTER_CRITICAL_SECTION(), you could do a more targeted interrupt disable by clearing all bits in the IER register except the one corresponding to the ADC interrupt and then restoring the original IER value when you exit the critical section. You would need to take care in your ADC ISR not to touch anything that needs to be protected by the critical section. Is that what you had in mind?

For your EPWM question, please create a separate thread so we can assign it to one of our EPWM experts.

Whitney