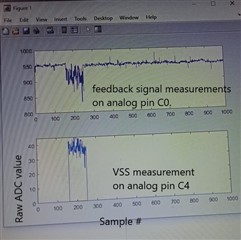

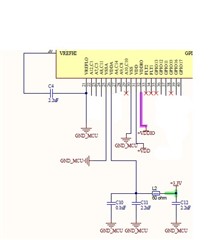

I am facing a strange issue with our power conversion board. The TMS320F280025C is driving some IGBTs and also doing analog measurements for the feedback signal. We are observing step changes in the feedback signals in somewhat periodic pattern while the oscilloscope view does not show any such pattern. While doing troubleshooting we decided to do some readings of the ground voltage i.e. VSS. There is an interesting observation that Vss measurement is also having step jumps exactly at the some points as the feedback signal. Since VSS, VSSA and VREFLO are all connected together so I am expecting that I should be getting zero voltage reading all the time. I am unable to understand why ADC is reading as large as 250 mV on this pin. The only thing that comes to my mind is that there could be some potential difference between VSS & VREFLO pins at some instants. We have used a 2.2 uF capacitor between VREFHI and VREFLO pins. The following circuit is implemented for ADC reference and power pins:

Please let me know if more details are required and help me in fixing the issue.