Other Parts Discussed in Thread: C2000WARE

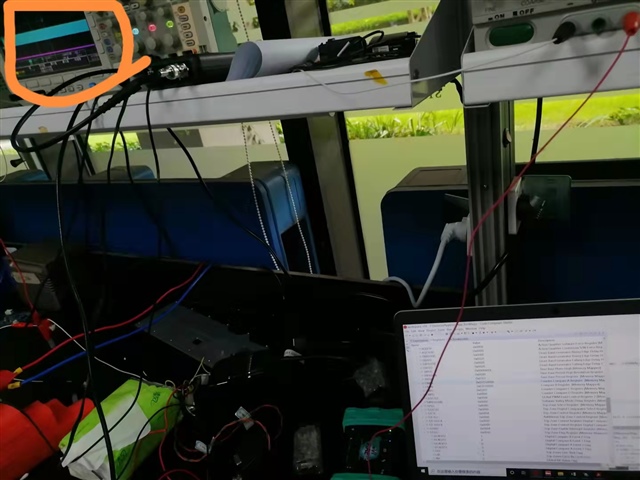

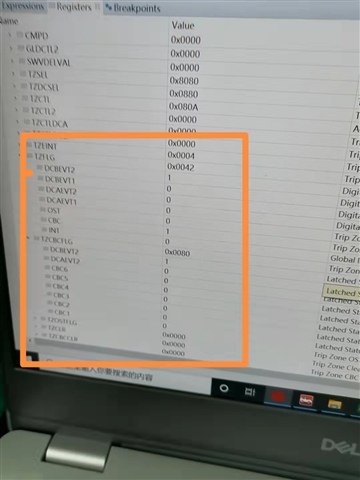

The TMS280049 is used, we configure the TZ module to shut PWM, TZ is from DCBEVT2 Cycle by Cycle.

most of the time, the pwm can shut and recover , BUT sometimes it can not shut PWM.

how to debug this problem?

it is set as :

EPWM_enableTripZoneSignals(base1, EPWM_TZ_SIGNAL_DCBEVT2);

EPWM_setTripZoneAction(base1, EPWM_TZ_ACTION_EVENT_DCBEVT2,EPWM_TZ_ACTION_LOW);

we set the voltage down to occur DCBEVT2 event. The DCBEVT2 occured, and I checked the TZFLG it has set to 1 (the TZFLG has cleared manually)

but the pwm is still running