I have a device that requires SPI mode 3 connected to my F2808 dev kit. (I have another device with SPI mode 0 and works great.)

The same issue exists for both SPI mode 1 or 3 so I will focus on SPI mode 1 and I am sure the issue will also be resolved for SPI Mode 3.

One other setup is that the data is in 4-bit mode (SPICCR.bit.SPICHAR) so the data shifting is considered. The data I will focus on is the F2808 sending a 0x901B4 to the external device.

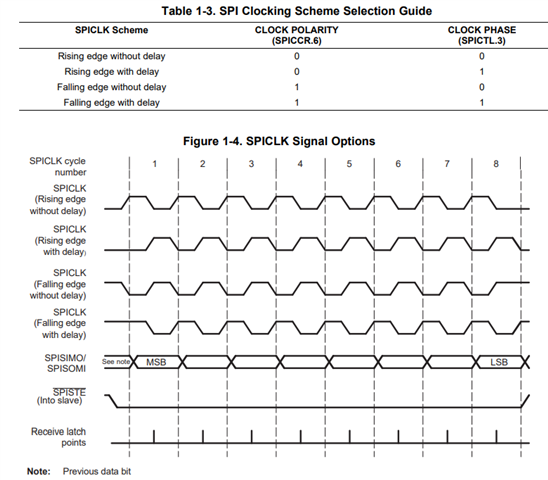

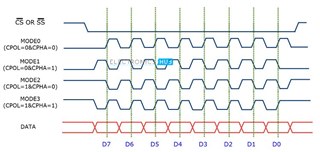

When in SPI Mode 0 or 2, the data shifts out as expected. See the TMC262_SPI_Mode0 attached image. However, when the SPI mode is changed to 1 or 3, the first SPI clock is occurring EXACTLY as the first data bit is transitioning from a high to a low of the 0x9 (1001b) and therefore is recognized as a 0 and then the rest of the data is off by 1 bit. See the TMC262_SPI_Mode1 image attached.

There is no difference in the clock setups as all device run a 1MHZ (SPIBRR = 0x0009, SysCtrlRegs.HISPCP.all = 0x0005, SysCtrlRegs.LOSPCP.all = 0x0005, SysCtrlRegs.XCLK.bit.XCLKOUTDIV=2).

Is there some setup I am over looking? The GPIO setup for the port is as follows:

GpioCtrlRegs.GPAPUD.bit.GPIO20 = 0; // Enable pull-up on GPIO20 (SPISIMOC)

GpioCtrlRegs.GPAPUD.bit.GPIO21 = 0; // Enable pull-up on GPIO21 (SPISOMIC)

GpioCtrlRegs.GPAPUD.bit.GPIO22 = 0; // Enable pull-up on GPIO22 (SPICLKC)

GpioCtrlRegs.GPAPUD.bit.GPIO23 = 0; // Enable pull-up on GPIO23 (SPISTEC)

/* Set qualification for selected pins to asynch only */

// This will select asynch (no qualification) for the selected pins.

// Comment out other unwanted lines.

GpioCtrlRegs.GPAQSEL2.bit.GPIO20 = 0; // Sysclock sync GPIO20 (SPISIMOC)

GpioCtrlRegs.GPAQSEL2.bit.GPIO21 = 0; // Sysclock sync GPIO21 (SPISOMIC)

GpioCtrlRegs.GPAQSEL2.bit.GPIO22 = 0; // Sysclock sync GPIO22 (SPICLKC)

GpioCtrlRegs.GPAQSEL2.bit.GPIO23 = 0; // Sysclock sync GPIO23 (SPISTEC)

/* Configure SPI-C pins using GPIO regs*/

// This specifies which of the possible GPIO pins will be SPI functional pins.

// Comment out other unwanted lines.

GpioCtrlRegs.GPAMUX2.bit.GPIO20 = 2; // Configure GPIO20 as SPISIMOC

GpioCtrlRegs.GPAMUX2.bit.GPIO21 = 2; // Configure GPIO21 as SPISOMIC

GpioCtrlRegs.GPAMUX2.bit.GPIO22 = 2; // Configure GPIO22 as SPICLKC

GpioCtrlRegs.GPAMUX2.bit.GPIO23 = 2; // Configure GPIO23 as SPISTEC