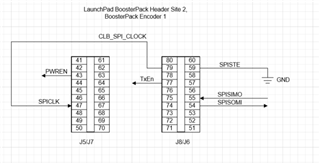

Other Parts Discussed in Thread: BOOSTXL-POSMGR, LAUNCHXL-F280049C

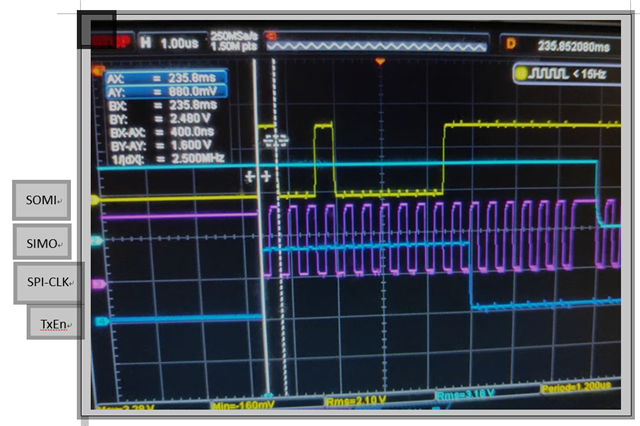

my LAUNCHXL-F280049C+BOOSTXL-POSMGR+TFORMAT can't work well. I find someone had same question, but I don't know how did he do?

my code :

1.

void PM_tformat_setupPeriph(uint32_t devLSPCLKFreq)//r

{

tformat_resetCLB();

tformat_initCLB1();

CLB_configLocalInputMux(CLB1_BASE, CLB_IN0, CLB_LOCAL_IN_MUX_GLOBAL_IN);

CLB_configLocalInputMux(CLB1_BASE, CLB_IN1, CLB_LOCAL_IN_MUX_GLOBAL_IN);

CLB_configLocalInputMux(CLB1_BASE, CLB_IN2, CLB_LOCAL_IN_MUX_GLOBAL_IN);

CLB_configLocalInputMux(CLB1_BASE, CLB_IN3, CLB_LOCAL_IN_MUX_GLOBAL_IN);

CLB_configLocalInputMux(CLB1_BASE, CLB_IN4, CLB_LOCAL_IN_MUX_GLOBAL_IN);

CLB_configLocalInputMux(CLB1_BASE, CLB_IN5, CLB_LOCAL_IN_MUX_GLOBAL_IN);

CLB_configLocalInputMux(CLB1_BASE, CLB_IN6, CLB_LOCAL_IN_MUX_GLOBAL_IN);

CLB_configLocalInputMux(CLB1_BASE, CLB_IN7, CLB_LOCAL_IN_MUX_GLOBAL_IN);

CLB_configGlobalInputMux(CLB1_BASE, CLB_IN0, CLB_GLOBAL_IN_MUX_EPWM4A);//r

CLB_configGlobalInputMux(CLB1_BASE, CLB_IN1, CLB_GLOBAL_IN_MUX_CLB_AUXSIG0);//

CLB_configGlobalInputMux(CLB1_BASE, CLB_IN2, CLB_GLOBAL_IN_MUX_EPWM4A);//

CLB_configGlobalInputMux(CLB1_BASE, CLB_IN3, CLB_GLOBAL_IN_MUX_EPWM4A);//

CLB_configGlobalInputMux(CLB1_BASE, CLB_IN4, CLB_GLOBAL_IN_MUX_EPWM4A);//

CLB_configGlobalInputMux(CLB1_BASE, CLB_IN5, CLB_GLOBAL_IN_MUX_EPWM4A);//

CLB_configGlobalInputMux(CLB1_BASE, CLB_IN6, CLB_GLOBAL_IN_MUX_EPWM4A);//

CLB_configGlobalInputMux(CLB1_BASE, CLB_IN7, CLB_GLOBAL_IN_MUX_EPWM4A);//

CLB_configGPInputMux(CLB1_BASE, CLB_IN0, CLB_GP_IN_MUX_GP_REG);

CLB_configGPInputMux(CLB1_BASE, CLB_IN1, CLB_GP_IN_MUX_EXTERNAL);

CLB_configGPInputMux(CLB1_BASE, CLB_IN2, CLB_GP_IN_MUX_EXTERNAL);

CLB_configGPInputMux(CLB1_BASE, CLB_IN3, CLB_GP_IN_MUX_EXTERNAL);

CLB_configGPInputMux(CLB1_BASE, CLB_IN4, CLB_GP_IN_MUX_EXTERNAL);

CLB_configGPInputMux(CLB1_BASE, CLB_IN5, CLB_GP_IN_MUX_EXTERNAL);

CLB_configGPInputMux(CLB1_BASE, CLB_IN6, CLB_GP_IN_MUX_EXTERNAL);

CLB_configGPInputMux(CLB1_BASE, CLB_IN7, CLB_GP_IN_MUX_GP_REG);//CLB_GP_IN_MUX_GP_REG

CLB_enableSynchronization(CLB1_BASE, CLB_IN0);

CLB_enableSynchronization(CLB1_BASE, CLB_IN1);

CLB_selectInputFilter(CLB1_BASE, CLB_IN0, CLB_FILTER_RISING_EDGE);

CLB_selectInputFilter(CLB1_BASE, CLB_IN1, CLB_FILTER_FALLING_EDGE);

tformat_initSPIFIFO(devLSPCLKFreq); // Initialize the SPI only

tformat_initCLBXBAR(); // Initialize the CLB XBARSPI only

}

2.

void PM_tformat_startOperation(void)//wenr

{

EALLOW;

HWREG(CLB1_BASE + CLB_LOGICCTL + CLB_O_LOAD_EN) |= CLB_LOAD_EN_GLOBAL_EN

| CLB_LOAD_EN_STOP;

__asm(" RPT #10 || NOP");

// CLB_setOutputMask(CLB1_BASE, 0x3C, true);

CLB_setOutputMask(CLB1_BASE, 0x3f, true);//r

__asm(" RPT #10 || NOP");

CLB_setGPREG(CLB1_BASE, 0x81);

}

3.

void tformat_setupGPIO(void) {

//

// GPIO1 is SPI Clk slave

//r

GPIO_setMasterCore(1, GPIO_CORE_CPU1);

GPIO_setPinConfig(GPIO_1_EPWM1_B);

//

// GPIO24 is the SPISIMOB

//r

GPIO_setMasterCore(24, GPIO_CORE_CPU1);

GPIO_setPinConfig(GPIO_24_SPIB_SIMO);

GPIO_setQualificationMode(24, GPIO_QUAL_ASYNC);

//

// GPIO31 is the SPISOMIB

//r

GPIO_setMasterCore(31, GPIO_CORE_CPU1);

GPIO_setPinConfig(GPIO_31_SPIB_SOMI);

GPIO_setQualificationMode(31, GPIO_QUAL_ASYNC);

//

// GPIO22 is the SPICLKB

//r

GPIO_setMasterCore(22, GPIO_CORE_CPU1);

GPIO_setPinConfig(GPIO_22_SPIB_CLK);

GPIO_setQualificationMode(22, GPIO_QUAL_ASYNC);

//

// GPIO27 is the SPISTEB

//r

GPIO_setMasterCore(27, GPIO_CORE_CPU1);

GPIO_setPinConfig(GPIO_27_SPIB_STE);

GPIO_setQualificationMode(27, GPIO_QUAL_ASYNC);

//

// GPIO7 is tformat TxEN

//r

GPIO_setMasterCore(7, GPIO_CORE_CPU1);

GPIO_setPinConfig(GPIO_7_OUTPUTXBAR5);

//

// GPIO28 is PwrEN

//r

GPIO_setMasterCore(28, GPIO_CORE_CPU1);

GPIO_setDirectionMode(28, GPIO_DIR_MODE_OUT);

}

4.

void tformat_configXBAR(void)

{

//

// Connect InputXbar-INPUT1 to GPIO24 - SPISIMO

//

XBAR_setInputPin(XBAR_INPUT1, 24);//r

XBAR_setCLBMuxConfig(XBAR_AUXSIG0, XBAR_CLB_MUX01_INPUTXBAR1);//InputXbar-INPUT1 TO XBAR_CLB_MUX01

XBAR_enableCLBMux(XBAR_AUXSIG0, XBAR_MUX01);

XBAR_setOutputMuxConfig(XBAR_OUTPUT5, XBAR_OUT_MUX01_CLB1_OUT4);//r

XBAR_enableOutputMux(XBAR_OUTPUT5, XBAR_MUX01);

}

5.

void tformat_configEPWM1(void) {

//

// Set the PWMA and B high as default values of tformat clk.

// Action on TZ1

//

EPWM_setTripZoneAction(EPWM1_BASE,

EPWM_TZ_ACTION_EVENT_TZA,

EPWM_TZ_ACTION_HIGH);

//

// Action on TZ1

//

EPWM_setTripZoneAction(EPWM1_BASE,

EPWM_TZ_ACTION_EVENT_TZB,

EPWM_TZ_ACTION_HIGH);

//

// Forces a Trip Zone event

//

EPWM_forceTripZoneEvent(EPWM1_BASE, EPWM_TZ_FORCE_EVENT_OST);

}

6.

#define TFORMAT_FREQ_DIVIDER 10