Other Parts Discussed in Thread: CONTROLSUITE

Dear team:

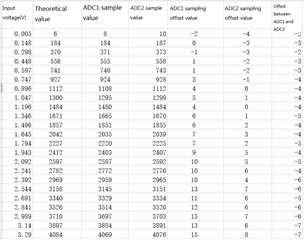

My customer uses the on-chip ADC1 and ADC2 for sampling testing with the following settings:

Use the routine in controlSUITE and modified as:

The input port of ADC1 is ADC1INB0

The input port of ADC2 is ADC2INB1

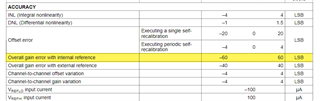

The test found that the values sampled by ADC1 and ADC2 are both smaller than the theoretical values, but the value of ADC2 is smaller in magnitude.

What could be causing the problem?

Best regards,

Green