Hello support,

I need some more details than I could find in "e2e.ti.com/.../tms320f280049-dac-to-adc-loopback-check-xbar-loopback

Especially, I need to focus better the difference between ADC loopback and OSDETECT (par. 13.9 of TRM).

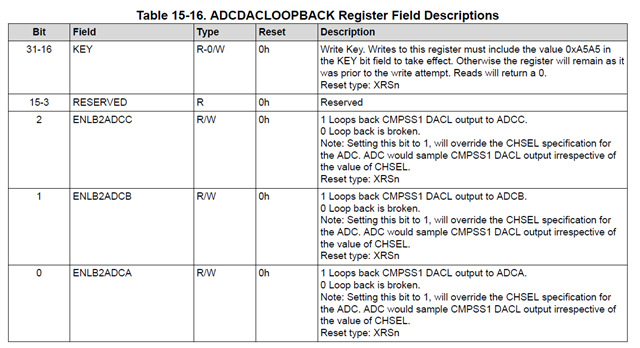

ADCDACLOOPBACK Register Field Descriptions in TRM of F280049C states for ENLB2ADCA, ENLB2ADCB, ENLB2ADCC:

"Setting this bit to 1, will override the CHSEL specification for the ADC. ADC would sample DACA output irrespective of the value of CHSEL."

What does it mean exactly ?

Setting ENLB2ADCC to 1 (together with KEY = 0xA5A5) creates an internal connection between DACA and the ADCC peripheral, so that I can read the DACA value from any ADCC ADCRESULTx register (when properly configured) ?

If so, can you confirm that with this strategy just the functionality of Sample+Hold circuit is tested, therefore reading a single ADCRESULTx is enough to know about the integrity of the ADCx S+H (reading more channels is useless) ?

On the other hand, OSDETECT circuitry is useful to detect situations of Open/Short inputs (but in this case I'm not testing microcontroller internal hardware, rather external connections) and in this case it is necessary to apply the strategy explained at par. 13.9 of TRM to all the channels that I need to guarantee?

best regards