Hello expert,

I am asking this question for our customer.

The customer uses TMS320f28377S, the CCS version and the compiler version are shown in the figure below.

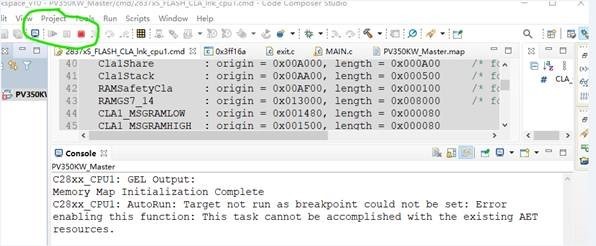

Customer find that when the uninitialized data is allocated, if the addresses assigned by .ebss, .esystem, .cio and .data contain addresses after 0x10000, the program cannot run, and the following figure will be displayed after debugging.

For example, in the following figure, .ebss, .esystem, .cio, and .data are allocated to addresses before 0x10000, which can be debugged normally.

For example, if .ebss, .esystem, .cio, and .data in the figure below are allocated to addresses after 0x10000, the problem mentioned above will occur.

Since I don't have the EVM of the F28277S, I used the F28379D for testing, and I can't reproduce the customer's problem. I noticed that CIO is displayed in the upper left corner of the console table. Is it a problem of .cio allocation? Could you please kindly help me analyze it? I'm attaching the customer's .cmd file below

// The user must define CLA_C in the project linker settings if using the

// CLA C compiler

// Project Properties -> C2000 Linker -> Advanced Options -> Command File

// Preprocessing -> --define

#define CLA_C

#ifdef CLA_C

// Define a size for the CLA scratchpad area that will be used

// by the CLA compiler for local symbols and temps

// Also force references to the special symbols that mark the

// scratchpad are.

CLA_SCRATCHPAD_SIZE = 0x200;

--undef_sym=__cla_scratchpad_end

--undef_sym=__cla_scratchpad_start

#endif //CLA_C

MEMORY

{

PAGE 0 :

/* BEGIN is used for the "boot to SARAM" bootloader mode */

D01SARAM : origin = 0x00BF00, length = 0x000100

RAMM0 : origin = 0x000122, length = 0x0002DE

Cla1Prog : origin = 0x008000, length = 0x002000

RAMGS0_6 : origin = 0x00C000, length = 0x007000

RESET : origin = 0x3FFFC0, length = 0x000002

/* Flash sectors */

BEGIN : origin = 0x084002, length = 0x000004

FLASH_HEAD : origin = 0x084000, length = 0x000002

FLASH_HEAD2 : origin = 0x084006, length = 0x000002

FLASHC_N : origin = 0x084008, length = 0x037FF8 /* on-chip Flash */

FLASH_SAFETY_CRC : origin = 0x0BC000, length = 0x000001

FLASH_SAFETY : origin = 0x0BC001, length = 0x003FFD

FLASH_TRAIL : origin = 0x0BFFFE, length = 0x000002

PAGE 1 :

BOOT_RSVD : origin = 0x000002, length = 0x000120 /* Part of M0, BOOT rom will use this for stack */

RAMM1 : origin = 0x000400, length = 0x000400

RAMD01 : origin = 0x00B000, length = 0x000F00

Cla1Share : origin = 0x00A000, length = 0x000A00 /* for CLA Data RAM */

Cla1Stack : origin = 0x00AA00, length = 0x000500 /* for CLA Stack Ram*/

RAMSafetyCla : origin = 0x00AF00, length = 0x000100 /* for CLA Stack Ram*/

RAMGS7_14 : origin = 0x013000, length = 0x008000 /* for Ram Data */

CLA1_MSGRAMLOW : origin = 0x001480, length = 0x000080

CLA1_MSGRAMHIGH : origin = 0x001500, length = 0x000080

RAMSafetyPrt : origin = 0x01B000, length = 0x000900

RAM_SAFETY_dwregister0 : origin = 0x01B900, length = 0x000002

RAM_SAFETY_dwregister1 : origin = 0x01B902, length = 0x000002

RAM_SAFETY_dwregister2 : origin = 0x01B904, length = 0x000002

RAM_SAFETY_wregister0 : origin = 0x01B906, length = 0x000001

RAM_SAFETY_wregister1 : origin = 0x01B907, length = 0x000001

RAM_SAFETY_wregistercheckFlag : origin = 0x01B908, length = 0x000001

RAMSafety : origin = 0x01B909, length = 0x0006F7

}

SECTIONS

{

/* Allocate program areas: */

.cinit : > FLASHC_N PAGE = 0, ALIGN(4)

.binit : > FLASHC_N PAGE = 0, ALIGN(4)

.pinit : > FLASHC_N, PAGE = 0, ALIGN(4)

.text : > FLASHC_N PAGE = 0, ALIGN(4)

codestart : > BEGIN PAGE = 0, ALIGN(4)

/* Initalized sections go in Flash */

.const : > FLASHC_N PAGE = 0, ALIGN(4)

.econst : > FLASHC_N PAGE = 0, ALIGN(4)

.switch : > FLASHC_N PAGE = 0, ALIGN(4)

.args : > FLASHC_N PAGE = 0, ALIGN(4)

/* Allocate uninitalized data sections: */

.stack : > RAMM1 PAGE = 1

.ebss : > RAMGS7_14 PAGE = 1

.esysmem : > RAMGS7_14 PAGE = 1

.cio : > RAMGS7_14 PAGE = 1

.data : > RAMGS7_14 PAGE = 1

#ifdef __TI_COMPILER_VERSION__

#if __TI_COMPILER_VERSION__ >= 15009000

.TI.ramfunc : {} LOAD = FLASHC_N,

RUN = RAMGS0_6,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

PAGE = 0, ALIGN(4)

#else

ramfuncs : LOAD = FLASHC_N,

RUN = RAMGS0_6,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

PAGE = 0, ALIGN(4)

#endif

#endif

ProgramRamFuncs : LOAD = FLASHC_N, /* Used by InitFlash() in SysCtrl.c */

RUN = RAMGS0_6,

LOAD_START(_ProgramRamFuncs_loadstart),

LOAD_END(_ProgramRamFuncs_loadend),

RUN_START(_ProgramRamFuncs_runstart)

PAGE = 0, ALIGN(4)

FPUmathTables : > FLASHC_N PAGE = 0

FlashSafetyCRC : > FLASH_SAFETY_CRC PAGE = 0

FlashSafety : > FLASH_SAFETY PAGE = 0

FlashHead : > FLASH_HEAD PAGE = 0

FlashHead2 : > FLASH_HEAD2 PAGE = 0

FlashTrail : > FLASH_TRAIL PAGE = 0

Cla1Prog : LOAD = FLASHC_N,

RUN = Cla1Prog,

RUN_START(_Cla1ProgRunStart),

LOAD_START(_Cla1ProgLoadStart),

LOAD_SIZE(_Cla1ProgLoadSize),

PAGE = 0, ALIGN(4)

CLAData : > Cla1Share, PAGE = 1

RAMSafetyForCla : > RAMSafetyCla, PAGE = 1

Cla1ToCpuMsgRAM : > CLA1_MSGRAMLOW, PAGE = 1

CpuToCla1MsgRAM : > CLA1_MSGRAMHIGH, PAGE = 1

RAMSafetyForPrt : > RAMSafetyPrt, PAGE = 1

RamSafety_dwregister0 : > RAM_SAFETY_dwregister0 PAGE = 1

RamSafety_dwregister1 : > RAM_SAFETY_dwregister1 PAGE = 1

RamSafety_dwregister2 : > RAM_SAFETY_dwregister2 PAGE = 1

RamSafety_wregister0 : > RAM_SAFETY_wregister0 PAGE = 1

RamSafety_wregister1 : > RAM_SAFETY_wregister1 PAGE = 1

RamSafety_wregistercheckFlag : > RAM_SAFETY_wregistercheckFlag PAGE = 1

// Must be allocated to memory the CLA has write access to

CLAscratch :

{ *.obj(CLAscratch)

. += CLA_SCRATCHPAD_SIZE;

*.obj(CLAscratch_end) } > Cla1Stack, PAGE = 1

.scratchpad : > Cla1Stack, PAGE = 1

.bss_cla : > Cla1Stack, PAGE = 1

.reset : > RESET, PAGE = 0, TYPE = DSECT /* not used, */

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/

Best Regards,

Julia