Dears,

My customer noticed all their ADC sampling value becomes higher when the prototype runs at higher PWM frequency. The are using internal reference, VREFHI pull to VSS with a 2.2uF capacitor.

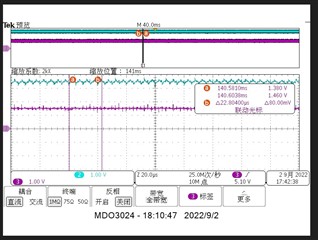

To identify the problem, I suggested them to measure the voltage VREFHI as we noticed the voltage on VrefHI dropped to ~1.1V. After changing 2.2uF to 4.7uF, the voltage raised to ~1.4V(as below picture), but still lower then expected.

As a comparison, here is a scope when high voltage power stage is not working:

May I know why the voltage on Vrefhi varies under different conditions? Is it a correct operation to measure VrefHI directly?

Regards,

Brian