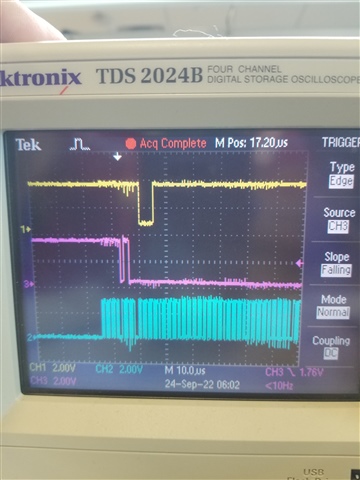

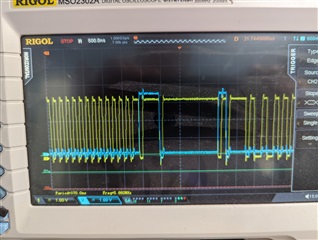

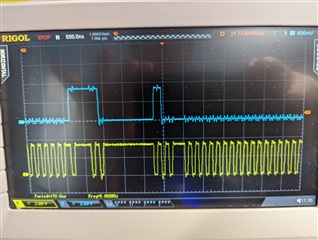

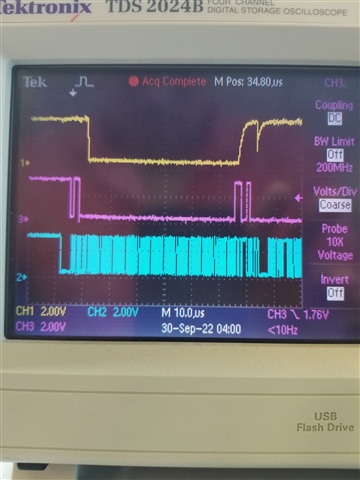

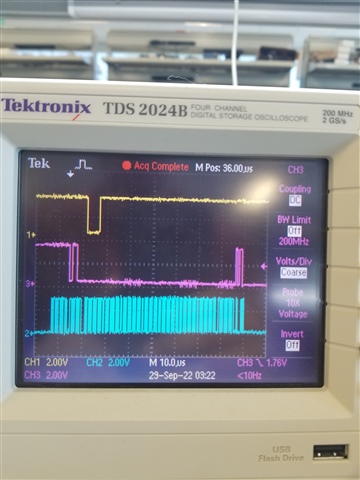

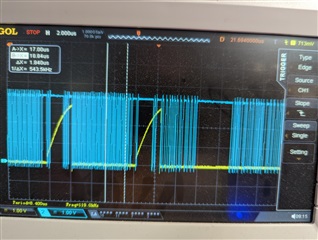

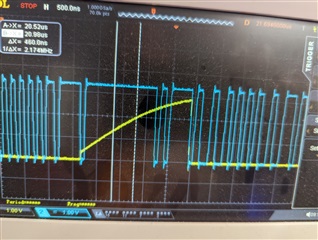

JTAG CLK - Blue Trace

JTAG TDO from DSP - Yellow.

I checked the 3V3 IO Rail and it is solid (no dips during transitions and is 3.29V).

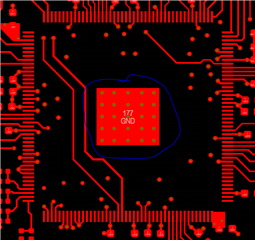

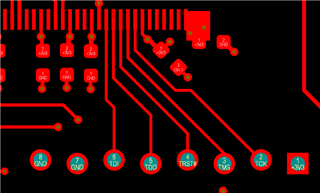

176-LQFP Package

It is possible that the assembly house did not solder the EP gnd pad properly. Does this look like the case here ?

TRST is HIGH btw