Other Parts Discussed in Thread: C2000WARE

Hi, is there an app note on how to implement the built in watch dog feature for the TMS320F28379S?

Thank

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi, is there an app note on how to implement the built in watch dog feature for the TMS320F28379S?

Thank

Many thanks...

I am using Simulink for the design and I have found a WD block which should work. From the datasheet the 8bit WD up-counter needs to be toggled every 255 counts of the main system clk (which is 16MHz), so every 16uSec. I assume if I just connect the WD block to a clk source that is at least16uSec/63KHz this should keep the WD happy and if the processor should lock up, this clk souce will stop and so so trigger a WD reset? Is this correct?

Thanks

No. I am afraid your understanding of how the WD operates is incorrect.

I assume if I just connect the WD block to a clk source that is at least16uSec/63KHz this should keep the WD happy and if the processor should lock up, this clk souce will stop and so so trigger a WD reset?

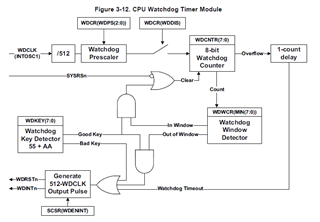

No, that is not how it works. The way to reset the WD is by writing a 0x55 followed by 0xAA to the WDKEY registers. Please refer to the TRM section for more information.

The C2000 Academy provides a simple and easy-to-understand module on WD and many other modules. WD is under C2000 System Control Modules. I encourage you to refer to the Academy material if you don't have the bandwidth to read the TRM chapter.

Hi Hareesh,

I'm using Simulink and I think all of the options regarding writing to the WDKEY registers are hidden and taken care of by the simulink block below and it seems all you need to do is add a clk to keep the WD happy. I'm assuming if I add a clk that toggles the WD i/p at at least 16uSec/63KHz this should keep the WD happy and if the uProc locks up the WD will reset the device?

Is this reasonable?

Thanks

Input frequency to the WD module is INTOSC1/512. Default pre-scaler value is /1. This is fed to a 8-bit counter.

10MHz/(512 x 256) = 76 Hz. This gives a rollover time of around 13.1 ms.

For questions pertaining to Simulink, please post in Mathworks forum.