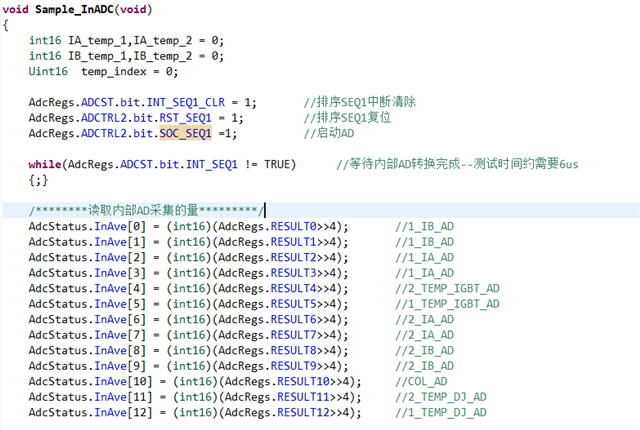

The software code is like this:

Software starts AD conversion, and then waits for SEQ1 sequence conversion completion flag INT_ SEQ1 to be set. Under normal circumstances, wait about 6us after starting AD conversion, AD conversion will be completed, and corresponding INT_ SEQ1 will also be set. However, INT_SEQ1 occasionally appears in practical applications is always not set, and the program falls into a dead cycle. Has anyone ever encountered this situation? What is the general reason?