Hi team,

Here's an issue from the customer may need your help:

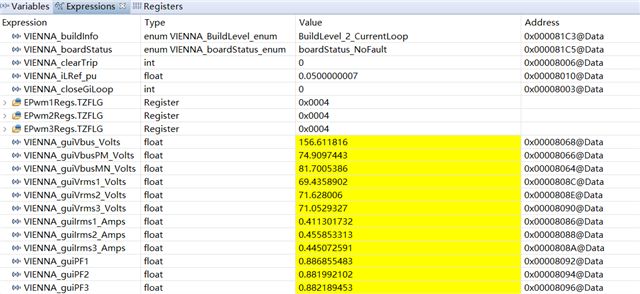

When the kit is loaded at 300 ohms, the input phase voltage is 70 V, and Bulid2 is established, and active rectification is not started. Monitoring the output with CCS is shown in the following figure:

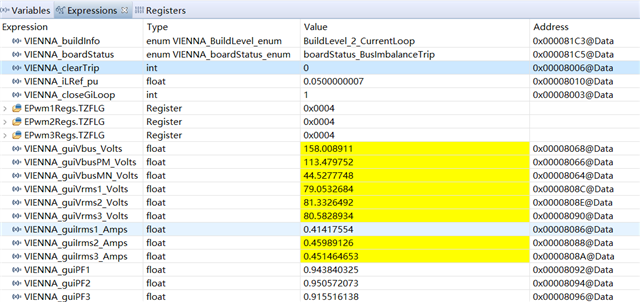

When active rectification is initiated, an imbalance in the upper and lower capacitor voltage values is detected, causing the protection feature to be triggered:

What could be the possible cause of this issue? Could you help check this case? Thanks.

Best Regards,

Cherry