Other Parts Discussed in Thread: PMP23126, , C2000WARE, LAUNCHXL-F280049C

Hi,

I implemented the code for phase-shifted full bridge by using example code of TIDM-02000 and PMP23126. The phase shift between legs are generated by events for PCMC.

This is a benchtop test on demo-board F280049C. I provide external DC signal to CMPPS high input and I used ramp generator in order implement PCMC.

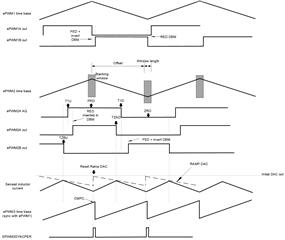

I generated 2xfrequency of ePWM8 in order generate SYNCPER signal in order sync. ePWMs and CMPSS. My main ePWMs are ePWM1,2. They are sync. to ePWM1.

(I use ePWM1,2,3,4 as PWM channels. All of them up-down count mode. ePWM5 and 6 -> SPI | ePWM7-> UART | ePWM8 as boot pin configuration. Pins are connected to 3.3V with pull-up resistor.)

I could obtain %100 duty cycle without any problem. However, at %0 duty cycle there is delay between ePWM channels.

I generate %0 duty by providing lower reference value to CMPSS internal DAC.

I generate %100 duty by providing higher reference value to CMPSS internal DAC.

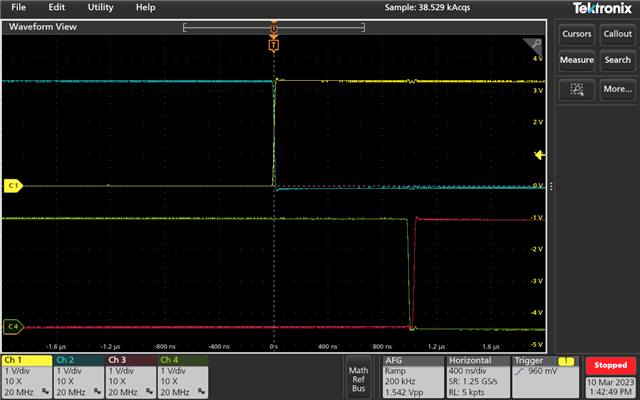

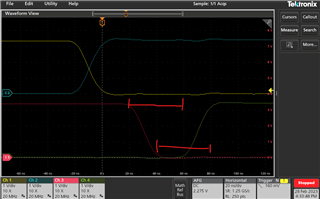

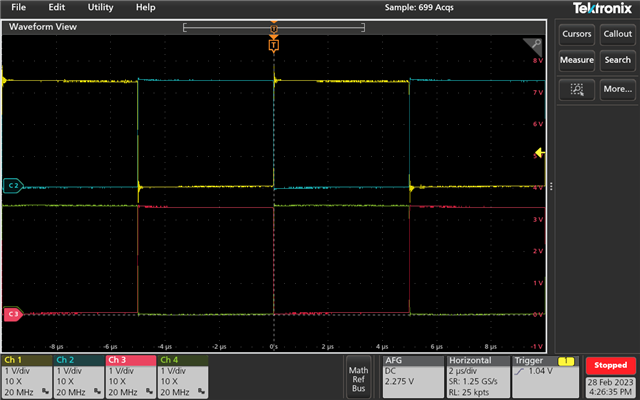

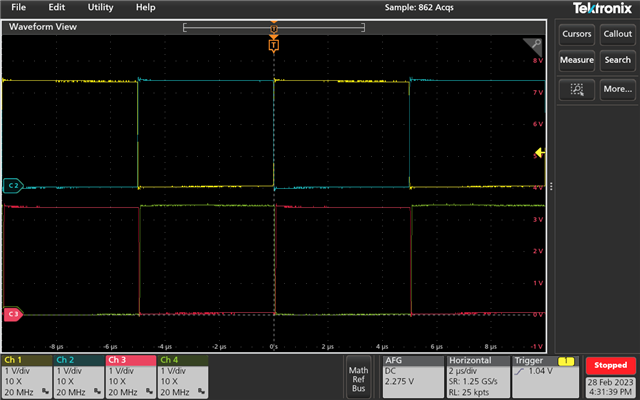

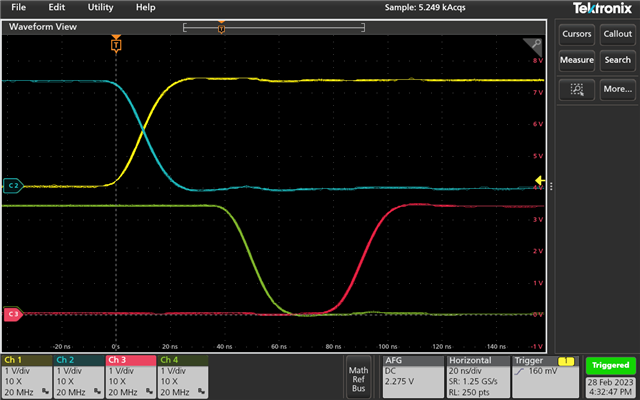

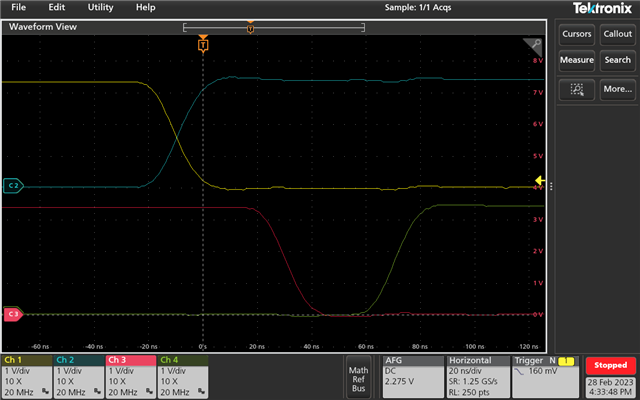

I inserted waveforms as below. Yellow 1A, Blue 1B, Red 2A, Green 2B

%100 duty cycle case in PSFB topology. There is %100 match on Yellow and Green! Deadband is 0 for all channels in order to see performance.

%0 duty cycle case in PSFB topology. There is %0 match on Yellow and Green! Deadband is 0 for all channels in order to see performance.

However, there is delay between rise and fall time between switches.

Details are as below.

1) Could you please explain how I could have %100 duty cycle and why not %0 duty cycle? What is the phenomenon behind?

As a remined, I don't use any filtering at CMPSS and I use blanking window at tripzone.

Sync. chain in ePWM timings might also be a problem... Blanking might be a problem....

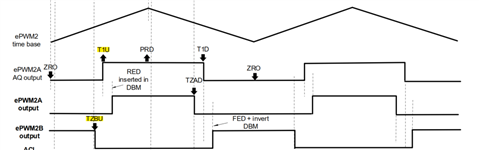

I have blanking at ePWM trip as below. I can provide more information if required.

// Set the blanking window offset in TBCLK counts

// An offset value in TBCLK counts is programmed

// which determines at what point after the CTR = PRD or CTR = 0 pulse the blanking window starts.

EPWM_setDigitalCompareWindowOffset(EPWM2_BASE, PeriodValue - 5);

// Set the blanking window length in TBCLK counts

// 10*TBLCK = 100nsec

EPWM_setDigitalCompareWindowLength(EPWM2_BASE, 10);