Other Parts Discussed in Thread: TIDM-02000

Hi,

I'm investigating the PMP23126 document. My questions are related to inner loop of PCMC with no SR case.

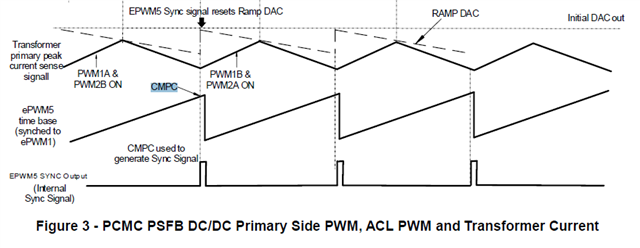

1) In figure 3 as below, CMPC signal is used as to generate SYNCPER signal. Could you please explain why designer choose CMPC instead of ZERO or PERIOD? EPWM5 can be easily sync to ePWM1 with setting 2 as phase shift on epwm5. It is then fully sync to ePWM1 and SYNCPER signal can be easily created at when TBCTR=ZERO. Could you please comment on it?

a) How do you decide the CMPC value? Is there any phase offset in the configuration of time-base counter for ePWM5 comparing to ePMW1. I didn't see related lines in software. Please, download from resource explorer?

b) Is CMPC equal to Period + dead-band of ePWM1B? It doesn't seem very well in the figure 3.

c) Do you update the value of CMPC when dead-band of ePWM1B is changed?

d) I downloaded the example code for PMP23126, however, I didn't see related lines to use EPWM5 and SYNCPER to sync for CMPSS module? Could you please show me where those lines?

e) Is there any delay time caused by SYNCPER signal to be monitored and qualified on CMPSS module?

f) What is the duty cycle range with event based phase shifting operation? Can I get %100 or %0 duty cycle? I also asked this question for TIDM-02000.

2) How do you decide the value of blanking window length and its offset? I think if I change the deadband in ePWM1, I should also update the window lenght? If yes, Could you please show me where those lines are written in software? I didn't see those lines in software. I can download new one if you guide me.

3) If I set 0 to the RAMPMAX to the internal DAC of CMPSS, is its output zero also in volts? Is there any minimum value when 0 is loaded?

Thanks in advance.