Hi experts,

I have a question about AQCTLA register.

When is SW updated value is active on the AQCTLA register ?

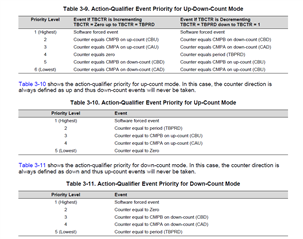

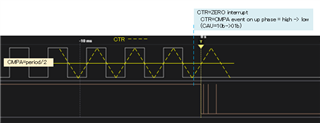

For example, our sw update a value on the AQCTLA register and what timing is new values(ZRO, PRD, CAD, CAU, ...) ?

EPwm1Regs.AQCTLA.all= 0x0090U

Is it immediately active ? or CTR=0 or CTR=PRD

Could you please let us know a timing to update active setting on AQ submodule ?

Best regards,

Hidehiko