Hello,

I want to capture the counter count value, when one of the DCAEVT1 occurs. The DCAEVT1 is happening twice in a cycle (up direction and down direction each (I am using PWM mode in up down mode)).

now I am reading the DCCAP register in one of the timer ISR, which is asynchronous to PWM counter. To get the capture count only when DCAEVT1 occurred in UP direction I am reading register only when EPwm1Regs.TBSTS.bit.CTRDIR = 0, the other configuration are as below,

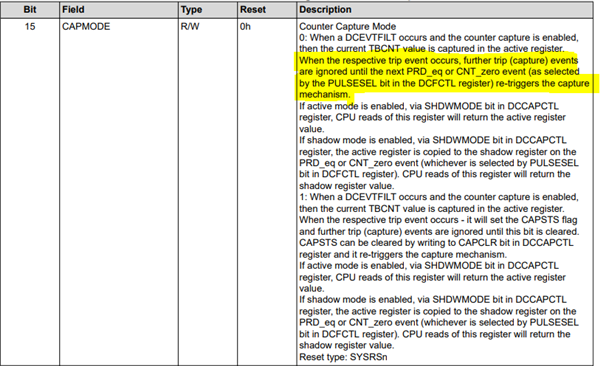

EPwm1Regs.DCCAPCTL.bit.SHDWMODE = 0;

EPwm1Regs.DCCAPCTL.bit.CAPMODE = 0;

Now as per my understanding if, EPwm1Regs.DCFCTL.bit.PULSESEL = 0, capture register will be updated at counter =PRD, hence gives count value for event happened when counter is in UP direction. but in this case it is giving some times count corresponding to when counter is in down direction.

while if EPwm1Regs.DCFCTL.bit.PULSESEL = 1, then it is giving correct result, don't know how as it is updating at ctr=Zero, is should provide count value corresponding to when counter down direction

Actually as per requirement, I need to use EPwm1Regs.DCFCTL.bit.PULSESEL = 2, with this configuration, it is not always capturing count value corresponding to when it is in UP direction.

pls let me know which configuration I need to use, to achieve count captured only during UP direction.

Thank you.