Other Parts Discussed in Thread: CCSTUDIO, UNIFLASH

Hi All,

We have an issue with flashing CPU1 of F28384D after it is initially flashed. The code seemed to be unchangeable.

Configuration:

SystemClock: 50Mhz (using the 10Mhz internal oscillator: INT_OSC2)

Programming method:

Both CCS12 or Matlab CodeGeneration (C2000)

Debugger:

XDS110

I have programmed both CPU1, and CPU2. I can change the CPU2 flash program, but for the CPU1 I can only program RAM.

The error that I am getting:

0 of 1 models built (1 models already up to date)

Build duration: 0h 0m 33.968s

The following error occurred during deployment to your hardware board:

Debug Server Scripting (DSS) error:

*** User inputs:

Target Configuration: C:\PROGRA~3\MATLAB\SUPPOR~1\R2022a\toolbox\target\SUPPOR~1\tic2000\CCS_CO~1\JAMES_~1.CCX

Program Name: C:\SY6632~1\SONA84~2.OUT

Board Name: *

CPU Name: C28xx_CPU1

Hardware Name: TI_F2838x_(C28x)

Boot From Flash: 1

*** Starting debug session...

C28xx_CPU1: GEL Output:

Memory Map Initialization Complete

C28xx_CPU1: GEL Output:

... DCSM Initialization Start ...

C28xx_CPU1: GEL Output:

... DCSM Initialization Done ...

C28xx_CPU1: GEL Output:

CPU2 is out of reset and configured to wait boot.

(If you connected previously, may have to resume CPU2 to reach wait boot loop.)

C28xx_CPU1: GEL Output:

CM is out of reset and configured to wait boot.

(If you connected previously, may have to resume CM to reach wait boot loop.)

C28xx_CPU1: If erase/program (E/P) operation is being done on one core, the other core should not execute from shared-RAM (SR) as they are used for the E/P code. User code execution from SR could commence after both flash banks are programmed.

C28xx_CPU1: Only CPU1 on-chip Flash Plugin can configure clock for CPU1, CPU2 and CM Flash operations. Plugin automatically configures PLL when CPU1 Flash operations are invoked. However, if users want to do only CPU2 or CM Flash operations without doing a prior CPU1 operation in the current session, they should click on 'Configure Clock' button in CPU1's on-chip Flash Plugin before invoking CPU2 and CM Flash operations. When this button is used, Flash Plugin will configure the clock for CPU1/CPU2 at 190MHz and CM at 95MHz using INTOSC2 as the clock source. Plugin will leave PLL config like this and user application should configure the PLL as required by application.

C28xx_CPU2: GEL Output:

Memory Map Initialization Complete

C28xx_CPU2: If erase/program (E/P) operation is being done on one core, the other core should not execute from shared-RAM (SR) as they are used for the E/P code. User code execution from SR could commence after both flash banks are programmed.

C28xx_CPU2: Only CPU1 on-chip Flash Plugin can configure clock for CPU1, CPU2 and CM Flash operations. Plugin automatically configures PLL when CPU1 Flash operations are invoked. However, if users want to do only CPU2 or CM Flash operations without doing a prior CPU1 operation in the current session, they should click on 'Configure Clock' button in CPU1's on-chip Flash Plugin before invoking CPU2 and CM Flash operations. When this button is used, Flash Plugin will configure the clock for CPU1/CPU2 at 190MHz and CM at 95MHz using INTOSC2 as the clock source. Plugin will leave PLL config like this and user application should configure the PLL as required by application.

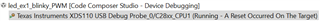

*** Debug Session Name: Texas Instruments XDS110 USB Debug Probe_0/C28xx_CPU1

*** Board Name: Texas Instruments XDS110 USB Debug Probe_0

*** CPU Name: C28xx_CPU1

*** Connecting to target...

SEVERE: Option not found

*** Warning: The clock backup and restore functionality is not supported with this CCS version. When using 'Boot from flash', perform a board power cycle after flashing to ensure that the program executes at the desired clock frequency.

C28xx_CPU1: GEL Output:

... DCSM Initialization Start ...

C28xx_CPU1: GEL Output:

... DCSM Initialization Done ...

C28xx_CPU1: GEL Output:

CPU2 is out of reset and configured to wait boot.

(If you connected previously, may have to resume CPU2 to reach wait boot loop.)

C28xx_CPU1: GEL Output:

CM is out of reset and configured to wait boot.

(If you connected previously, may have to resume CM to reach wait boot loop.)

*** Loading the program to the target...

C28xx_CPU1: GEL Output:

... DCSM Initialization Start ...

C28xx_CPU1: GEL Output:

... DCSM Initialization Done ...

C28xx_CPU1: GEL Output:

CPU2 is out of reset and configured to wait boot.

(If you connected previously, may have to resume CPU2 to reach wait boot loop.)

C28xx_CPU1: GEL Output:

CM is out of reset and configured to wait boot.

(If you connected previously, may have to resume CM to reach wait boot loop.)

C28xx_CPU1: GEL Output:

... DCSM Initialization Start ...

C28xx_CPU1: GEL Output:

... DCSM Initialization Done ...

C28xx_CPU1: GEL Output:

CPU2 is out of reset and configured to wait boot.

(If you connected previously, may have to resume CPU2 to reach wait boot loop.)

C28xx_CPU1: GEL Output:

CM is out of reset and configured to wait boot.

(If you connected previously, may have to resume CM to reach wait boot loop.)

SEVERE: C28xx_CPU1: Trouble Removing Breakpoint with the Action "Remain Halted" at 0xd148: (Error -1066 @ 0xD148) Unable to set/clear requested breakpoint. Verify that the breakpoint address is in valid memory. (Emulation package 9.5.0.00143)

SEVERE: C28xx_CPU1: Error executing PLL configuration algorithm. Operation cancelled. (0x0)

SEVERE: C28xx_CPU1: File Loader: Memory write failed: Unknown error

SEVERE: C28xx_CPU1: GEL: File: C:\SY6632~1\SONA84~2.OUT: Load failed.

SEVERE: File: C:\SY6632~1\SONA84~2.OUT: Load failed.

SEVERE: Error loading "C:\SY6632~1\SONA84~2.OUT": File: C:\SY6632~1\SONA84~2.OUT: Load failed.

org.mozilla.javascript.WrappedException: Wrapped com.ti.ccstudio.scripting.environment.ScriptingException: Error loading "C:\SY6632~1\SONA84~2.OUT": File: C:\SY6632~1\SONA84~2.OUT: Load failed. (C:\PROGRA~3\MATLAB\SUPPOR~1\R2022a\toolbox\shared\SUPPOR~1\tic2000/CCS_CO~1/RUNPRO~1.JS#169)

at org.mozilla.javascript.Context.throwAsScriptRuntimeEx(Context.java:1693)

at org.mozilla.javascript.MemberBox.invoke(MemberBox.java:160)

at org.mozilla.javascript.NativeJavaMethod.call(NativeJavaMethod.java:204)

at org.mozilla.javascript.optimizer.OptRuntime.call1(OptRuntime.java:66)

at org.mozilla.javascript.gen.c1._c0(C:\PROGRA~3\MATLAB\SUPPOR~1\R2022a\toolbox\shared\SUPPOR~1\tic2000/CCS_CO~1/RUNPRO~1.JS:169)

at org.mozilla.javascript.gen.c1.call(C:\PROGRA~3\MATLAB\SUPPOR~1\R2022a\toolbox\shared\SUPPOR~1\tic2000/CCS_CO~1/RUNPRO~1.JS)

at org.mozilla.javascript.ContextFactory.doTopCall(ContextFactory.java:340)

at org.mozilla.javascript.ScriptRuntime.doTopCall(ScriptRuntime.java:2758)

at org.mozilla.javascript.gen.c1.call(C:\PROGRA~3\MATLAB\SUPPOR~1\R2022a\toolbox\shared\SUPPOR~1\tic2000/CCS_CO~1/RUNPRO~1.JS)

at org.mozilla.javascript.gen.c1.exec(C:\PROGRA~3\MATLAB\SUPPOR~1\R2022a\toolbox\shared\SUPPOR~1\tic2000/CCS_CO~1/RUNPRO~1.JS)

at org.mozilla.javascript.tools.shell.Main.evaluateScript(Main.java:503)

at org.mozilla.javascript.tools.shell.Main.processFileSecure(Main.java:425)

at org.mozilla.javascript.tools.shell.Main.processFile(Main.java:391)

at org.mozilla.javascript.tools.shell.Main.processSource(Main.java:382)

at org.mozilla.javascript.tools.shell.Main.processFiles(Main.java:179)

at org.mozilla.javascript.tools.shell.Main$IProxy.run(Main.java:100)

at org.mozilla.javascript.Context.call(Context.java:528)

at org.mozilla.javascript.ContextFactory.call(ContextFactory.java:450)

at org.mozilla.javascript.tools.shell.Main.exec(Main.java:162)

at com.ti.ccstudio.apps.internal.scripting.RunScript$1.run(RunScript.java:89)

Caused by: com.ti.ccstudio.scripting.environment.ScriptingException: Error loading "C:\SY6632~1\SONA84~2.OUT": File: C:\SY6632~1\SONA84~2.OUT: Load failed.

at com.ti.debug.engine.scripting.Memory.loadProgram(Memory.java:932)

at java.base/jdk.internal.reflect.NativeMethodAccessorImpl.invoke0(Native Method)

at java.base/jdk.internal.reflect.NativeMethodAccessorImpl.invoke(Unknown Source)

at java.base/jdk.internal.reflect.DelegatingMethodAccessorImpl.invoke(Unknown Source)

at java.base/java.lang.reflect.Method.invoke(Unknown Source)

at org.mozilla.javascript.MemberBox.invoke(MemberBox.java:145)

... 18 more

SEVERE: C28xx_CPU1: Trouble Setting Breakpoint with the Action "Remain Halted" at 0xd058: (Error -1066 @ 0xD058) Unable to set/clear requested breakpoint. Verify that the breakpoint address is in valid memory. (Emulation package 9.5.0.00143)

WARNING: C28xx_CPU1: Breakpoint Manager: Retrying with a AET breakpoint

Thank you for your kind support.