Hi champs,

My customer wants to use the oscilloscope to measure the arriving time EtherCAT slave receives SYNC or PDO packets from master side.

Can ESC toggle I/O when receiving SYNC or PDO packets?

Thanks and regards,

Luke

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi champs,

My customer wants to use the oscilloscope to measure the arriving time EtherCAT slave receives SYNC or PDO packets from master side.

Can ESC toggle I/O when receiving SYNC or PDO packets?

Thanks and regards,

Luke

Hi Luke,

They are wanting to view IO toggles right when the frames are received? Sync and PDO ISRs could be used for this, but I believe that would be after the F2838x ESC processes the frame.

Let me look into this some more.

Best,

Kevin

Hi Luke,

The ESC_SYNC0/1 signals (MUX option) can be used to bring-out the sync signal.

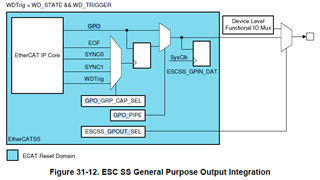

ESC GPO can bring out the internal signals shown in the diagram below:

Best,

Kevin

Kevin,

Do customers get this SYNC signal output by configuring GPIO MXU?

Do they need to modify the EEPROM contents please?

Regards,

Luke

Hi Luke,

Do customers get this SYNC signal output by configuring GPIO MXU?

It will require GPIO MUX config and ESC register configuration as well (i.e. EtherCAT IP Core).

Do they need to modify the EEPROM contents please?

No, I don't see any configuration related to this in the EtherCAT Slave Information (ESI) specs.

Best,

Kevin

Kevin,

No problem for GPIO MUX configuration, but I believe that customers get difficulty to modify ESC registers for this function.

Do you know which ESC registers customers should take care of please?

Regards,

Luke

Hi Luke,

I believe the ESC register would be SYNC Out Unit in Table 110: Register Activation register (0x0981) of the Beckhoff spec. However, I believe this register will be set by the EtherCAT master when DC sync is configured.

The 'f2838x_cpu1_echoback_solution' has the SW configuration for the SYNCx pins already.

// External Connections // - The controlCARD RJ45 port 0 is connected to PC running TwinCAT master // - If distributed clocks enabled, connect and observe SYNC0/1 signals on // GPIO127 and GPIO128

You can follow the same Sitara instructions below for configuring DC in TwinCAT.

Best,

Kevin

Kevin,

According to my customer, the machine is working in CSP mode and host transmits data to F28388D device. However, my customer doesn't see any signal output at SYNC0/1 pins.

How should my customer debug this problem please?

Regards,

Luke

Hi Luke,

Are they using 'f2838x_cpu1_cia402_solution' example currently, and they've enabled DC sync mode?

Can they try with the 'f2838x_cpu1/cm_echoback_solution' instead?

Best,

Kevin

Hi Luke,

They can take a look at section 9.2.3 SyncSignal Generation of Hardware Data Sheet Section I for relevant ESC registers and SII configuraiton.

Do they see Sync0_Isr entered when debugging their code?

Best,

Kevin