Hi Team,

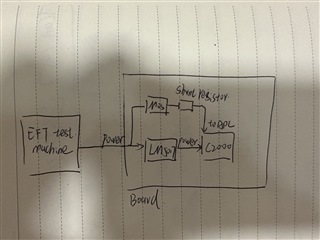

Customer use 64pin F280025 to control a stepper. Customer sample the shunt resistor with the ADC in MCU.

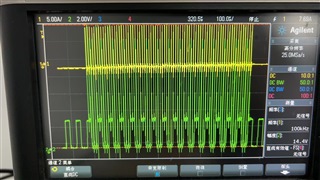

But they found the motor will jitter,when EFT test(2000V, 5kHz/100kHz, 75 pulse each 300ms). We watch the waveform in oscilloscope.

we found phase current is not very smooth(the yellow), and the PWM duty cycle is change(the green). AI pin for ADC might over 3.6V during the EFT test.

Customer use the software reference to control the PWM, the motor won't jitter.

If make a filter to delete the outliers form AD sampling, there will be over-current in their board.

Without EFT test, the motor preform well. And customer also use 80pin F280025 in another product, there is no that problem in EFT test.

Add some TVS isn't change the result, and add GPIO filtter in software also not change the result.

And we test other customer's product(stepper contorl by 280025) there is also the same probem.

But in customer last platform 28034, there is also no problem. The 280025 and 28034 is almost the same design.

Do you have any idea to solve the problem?

Thanks alot.