Other Parts Discussed in Thread: C2000WARE, SYSCONFIG

Hello All,

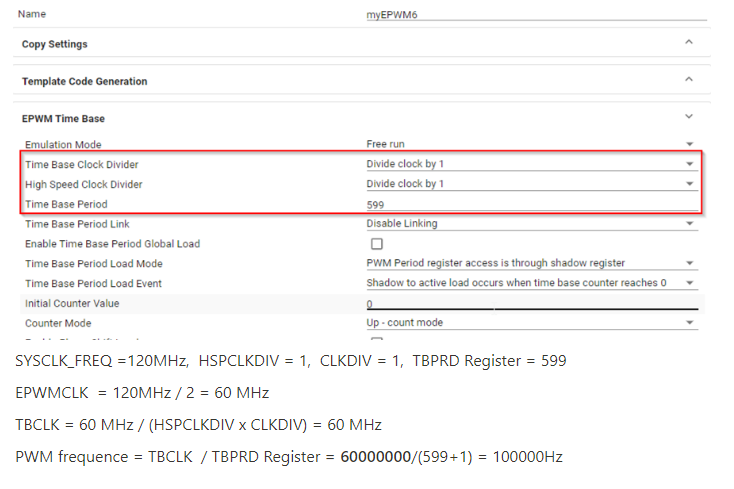

In our design, the EPWMCLK is 60MHz, and We have 100KHz EPWM frequence output.

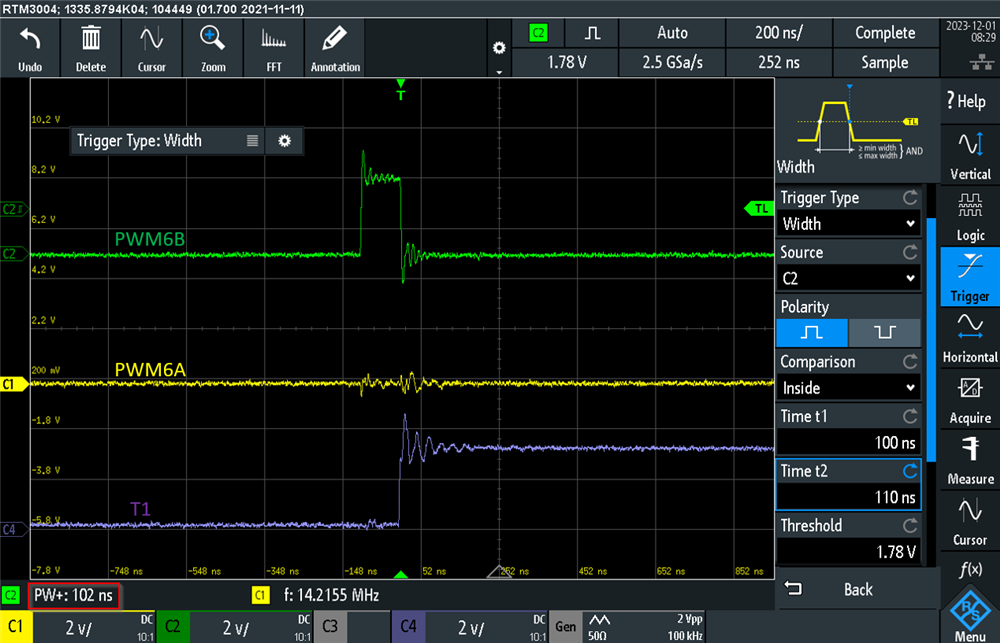

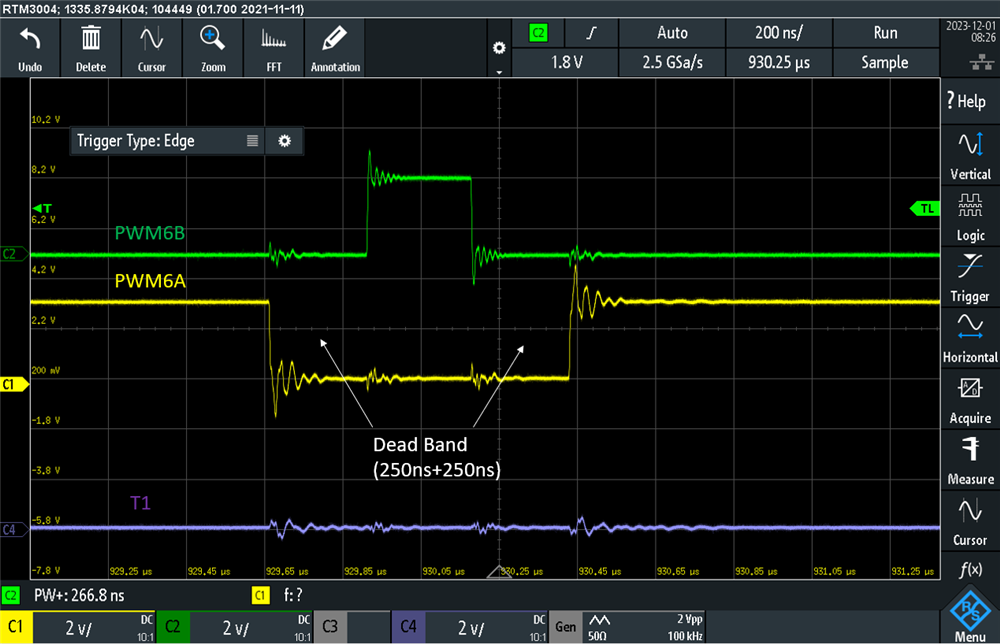

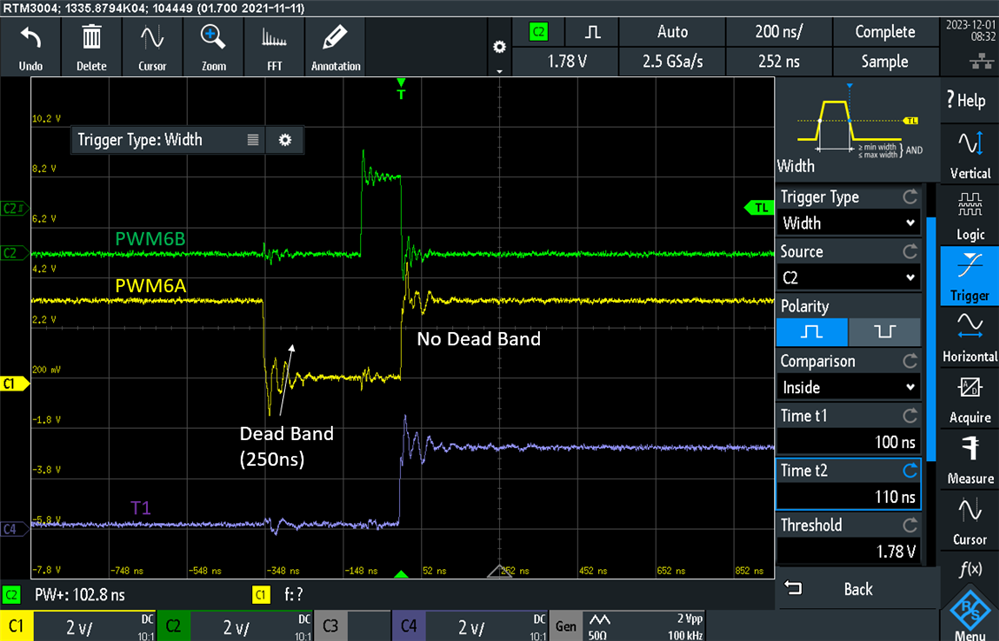

I'll like to use the T1 event to reduce the ePWM duty in AQ module. The T1 event is from CMPSS → CTRIPH → X-bar → ePWM DC module → DCAEVT1.

I have disabled the sync mode.

I can reduce the ePWM duty, but I always got a 16ns step to reduce the duty.

For example, I have reduced the the PWM duty with a 100ns plus width , then I move the T1 signal 4ns ahead, and I still get a 100ns plus width. It can not be reduce to 96ns plus width.

If I move the compare signal 16ns ahead, I can get a PWM+ with 84ns. Is it possible to improve it ?