Tool/software:

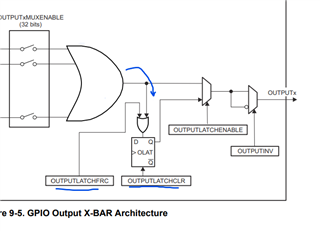

I am using OUTPUT XBAR and I am passing a CMPSS trip out to it. The CMPSS CTRIPOUTH is 1 and this is passed to the OUTPUTx via the D Latch for OUTPUT XBAR

Here is my problem: When I try to clear the LATCH output via OUTPUTLATCHCLR register, it remains 1 as is and does not clear out.

When I disable the OUTPUTxMUXENABLE register and then clear the latch via setting OUTPUTLATCHCLR to 1, it gets cleared.

For the D latch, the expected behavior is that when OUTPUTLATCHCLR is set to 1, the output gets cleared regardless of the clock or data input. But here, I see that it gets cleared only when the input is set to 0. It is not cleared when input is 1.

Is this correct behavior or am I understanding things incorrectly?

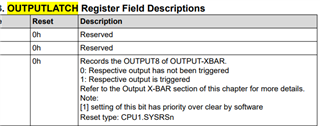

I also saw that the following is written for the OUTPUTLATCH register:

Does it mean that if the input setting is '1' for the latch, it has a higher priority over clearing the latch output using OUTPUTLATCHCLR?

Does it mean that if the input is 1, we cannot clear the latch using OUTPUTLATCHCLR, and only when the input is 0, we can clear it? Won't this defeat the purpose of the D latch?