Hi

Please help me with the setting of acceptance masks for eCAN in F28335

How and where are they set?

Any help would be appreciated.

Thanks & Regards

Sneha

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi

Please help me with the setting of acceptance masks for eCAN in F28335

How and where are they set?

Any help would be appreciated.

Thanks & Regards

Sneha

In F28335, acceptance masks can be set in LOCAL ACCEPTANCE MASK REGISTER.

Mask depends on number of bits of message identifier to be checked (compared) for acceptance of message.

1 (Logic High) --> Enable checking (comparing) of bit in message identifier

0 (Logic Low) --> Disable checking (comparing) of bit in message identifier

e.g.

For 11-bit standard message identifier,

if mask is 01110000000, then bits 10, 9 and 8 of incoming message will be checked (compared) for acceptance of message.

Thank you,

Sunil Sawant

Thanks Sunil

I will have a look into it.

Any idea if in CANES register bit error flag is set,how to resolve it?

thanks & regards

Sneha

In F28335 eCAN, BIT ERROR FLAG in CANES REGISTER is set when electrical voltage levels on CAN bus (CAN_H and CAN_L) are incorrect.

This is a Physical Layer problem (Layer 1 of OSI Model).

It seems electrical signal voltage levels on CAN bus (CAN_H and CAN_L) are not correct or are not correctly detected by eCAN module of F28335. eCAN module in F28335 is expecting certain voltage levels on CAN_H and CAN_L and is not getting those levels.

Please see datasheet and ensure electrical signal voltage levels are correct as those mentioned in datasheet.

Also, ensure the termination resistor between CAN_H and CAN_L lines is 120E.

Bit errors are mostly related to electrical problems and less related to logical errors.

Thank you,

Sunil Sawant

Hi Sunil

Thanks for your patient replies.

I am working on F28335 and using ISO1050 EVM as CAN transciever,which has on board terminating resistance.SO i need not worry about that.

The problem am facing is that I am trying to establish communication using CAN by running control suite example program ecan a-b-xmit.But am not getting the expected CANH and CANl waveforms nor do I recieve something.

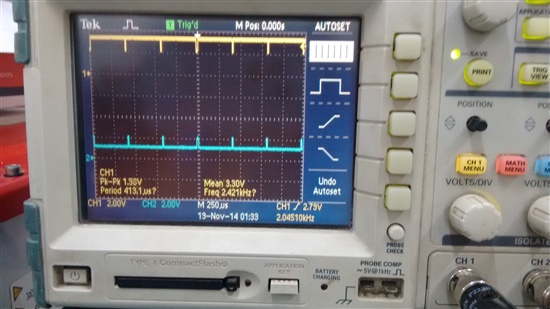

I get CANH and CANL waveforms like below:

Frequency is 2.5 kHZ but they sometime and then are gone.If I terminate program rebuild again,I do not get them till the system is off for certain minimum amount of time and started again.

When I check the registers sometimes CANES...BE is set and at other times SE is set:

1. eCANA- TX at one time

2.eCANb-Tx at other time checked later on

3. eCANB-Rx

obviously the transmission is not taking place and I am really stuck at it.Please spare you time to look into this.

I would really be grateful to you.

thanks & Regards

Sneha

I need some time to carefully study and analyze the images of CRO screenshot and Code Composer Studio Watch Window / Register Window.

I will reply after i carefully study and analyze the images.

Thank you,

Sunil Sawant

HI Sunil

Thank You so much.

There is one open post for this at

http://e2e.ti.com/support/microcontrollers/c2000/f/171/p/382724/1363343.aspx#1363343

which was posted earlier,but with no successful answers as of now.

I really wait for your opinion and help.

Thanks & Regards

Sneha

I have following observations:

1. You are using single-ended probe for observing CAN Bus waveforms on CRO.

CAN Bus functions on differential signalling at physical layer.

i.e., CAN Bus transceiver detects and interprets (calculates / understands) difference between CAN_H and CAN_L signal levels and decides whether data on CAN Bus is Dominant or Recessive (Logic 1 or Logic 0).

You may not be able to correctly measure / observe signal voltage levels on CAN Bus (which is differential) using single-ended probe. You should use differential probe for observing / measuring CAN Bus signals correctly on CRO.

Above argument is also applicable for measuring frequency / bit-rate of CAN data on CRO. Frequency / Bit-Rate of CAN data cannot be measured correctly using single-ended probe on CRO.

2. I think you are missing out some basic steps to configure and use eCAN in F28335.

I have few suggestions about eCAN in F28335.

Configuring eCAN in F28335.

Following steps should be followed while programming eCAN in F28335:

Step 1. Configure SysCtrl module in F28335. SysCtrl module configures clock PLL in F28335 and sets main clock frequency in F28335.

Step 2. Configure I/O pins on F28335 to connect eCAN peripheral to I/O pins of F28335. Else I/O pins are connected to GPIOs on F28335.

Step 3. Configure CAN Protocol Kernel (CPK) in F28335 eCAN module.

This is done by deciding bit-rate of data on CAN bus.

Refer SPRUEU1.pdf file --> page 68. Download the file from TI website.

Step 4. Configure Message Controller in F28335 eCAN module.

This is done by configuring mailboxes for transmit and receive operations.

Refer SPRUEU1.pdf file --> page 72. Download the file from TI website.

Above 4 steps should configure eCAN in F28335 for normal operation.

eCAN module testing / debugging tips:

1. Isolate the problem.

First check whether problem is hardware / electrical or software / logical.

Always start by checking for hardware / electrical problems and then move to checking software / logical problems. This is because, unless you have flawlessly functioning hardware, you cannot develop software for making hardware operational. In your case it is eCAN in F28335.

From your earlier and recent posts, clear information is not available about your eCAN test set-up hardware and software for configuring and using eCAN.

If possible provide this information for gaining complete understanding of your system.

Also, initially do not program Acceptance Masks in eCAN in F28335.

Acceptance Masks are used by CAN receiver for filtering messages from multiple transmitters on CAN bus.

You should disable Acceptance Masks in eCAN in F28335.

Data could be received in eCAN in F28335 without Acceptance Masks.

Only problem is you will receive all messages and filtering of messages would be disabled.

Hi Sunil

Thanks for the elaborate answer.

1. I had earlier tested my CAN transciever for CANH and CANL waveforms with single ended probes on two channels of DSO and I didn't face any issues.

The voltage level and frequency were correct.Thats why I am using the same now.

So,if thats the case I will try checking this out.

2. About the configuration i have gone though it again and again.But chances are always there that I missed out on something.Therefore,Keeping in mind the steps given by you,I will again try looking at the code and the configuration steps.

3.The test setup:

CCS V6.0

Experimenter kit TMS320F28335

Isolated DSO

CAN Transceiver ISO1050EVM

Control suite program- eCAN A to B xmit

CAN A - GPIO19 = CANTX,GPIO18 = CANRX

CAN B-GPIO8 = CANTX,GPIO10 =CANRX

For now,I am trying to check the CANH and CANL waveforms without connecting back to CAN module B which is receiver.

CAN module A = transmitter,GPIO19 is connected to TXD pin of ISO1050 and then I am trying to check the waveforms for CANH and CANL.Doing this gives me the waveforms I shared before but sometimes,not everytime.

Even if I connect it to reciever :

CANA- ISO1050 (1) -ISO1050 (2) -CANB

I donot observe anything with the can registers.

4. LAM registers are not programmed in the example program given as to what I have understood they are required in SCC mode of CAN.But here I am using it in normal mode,so they aren't required.

Please point to where I am wrong.

And I am looking into the steps mentioned by you.Will let you know my observations But guess TI website is down tomorrow for maintenance.

Therefore I will try to answer tonight as soon as possible.

Thanks & Regards

Sneha

From your recent post, i observe you are unable to isolate the problem. i.e. you are unable to understand the nature of problem, whether the problem is in hardware or software.

I suggest a quick tip to isolate the problem.

eCAN in F28335 can be operated in Self-Test Mode. In Self-Test mode, transmitted data (TXBUF) is looped-back to RXBUF internally inside eCAN in F28335. So data does not come out on CAN_H and CAN_L pins of F28335. This eliminates the possibility of hardware error and you can focus entirely on software part of configuring and using eCAN in F28335.

eCAN in F28335 can be operated in Self-Test mode, by setting STM bit in MASTER CONTROL REGISTER. Refer to F28335 eCAN user guide for details.

Once eCAN in F28335 works Self-Test mode, you can be confident about software. Later you can disable Self-Test mode and allow data to come out on CAN bus. Now if there are errors, you can focus on hardware only, because your software is already proven in Self-Test mode.

I have attached a program to operate eCAN in Self-test mode. You will have to modify the program to suit your application requirements.

Inform me about the result of program execution.

File Name: eCAN Loop-Back using SelfTest.txt

Hi Sunil

1.Can loopback:

// TI File $Revision: /main/2 $

// Checkin $Date: July 30, 2009 18:44:23 $

//###########################################################################

//

// FILE: Example_2833xECanBack2Back.c

//

// TITLE: DSP2833x eCAN Back-to-back transmission and reception in

// SELF-TEST mode

//

// ASSUMPTIONS:

//

// This program requires the DSP2833x header files.

//

// This progrm uses the peripheral's self test mode.

// Other then boot mode configuration, no other hardware configuration

// is required.

//

// As supplied, this project is configured for "boot to SARAM"

// operation. The 2833x Boot Mode table is shown below.

// For information on configuring the boot mode of an eZdsp,

// please refer to the documentation included with the eZdsp,

//

// $Boot_Table:

//

// GPIO87 GPIO86 GPIO85 GPIO84

// XA15 XA14 XA13 XA12

// PU PU PU PU

// ==========================================

// 1 1 1 1 Jump to Flash

// 1 1 1 0 SCI-A boot

// 1 1 0 1 SPI-A boot

// 1 1 0 0 I2C-A boot

// 1 0 1 1 eCAN-A boot

// 1 0 1 0 McBSP-A boot

// 1 0 0 1 Jump to XINTF x16

// 1 0 0 0 Jump to XINTF x32

// 0 1 1 1 Jump to OTP

// 0 1 1 0 Parallel GPIO I/O boot

// 0 1 0 1 Parallel XINTF boot

// 0 1 0 0 Jump to SARAM <- "boot to SARAM"

// 0 0 1 1 Branch to check boot mode

// 0 0 1 0 Boot to flash, bypass ADC cal

// 0 0 0 1 Boot to SARAM, bypass ADC cal

// 0 0 0 0 Boot to SCI-A, bypass ADC cal

// Boot_Table_End$

//

// DESCRIPTION:

//

// This test transmits data back-to-back at high speed without

// stopping.

// The received data is verified. Any error is flagged.

// MBX0 transmits to MBX16, MBX1 transmits to MBX17 and so on....

// This program illustrates the use of self-test mode

//

//###########################################################################

// Original Author H.J.

//

// $TI Release: 2833x/2823x Header Files V1.32 $

// $Release Date: June 28, 2010 $

//###########################################################################

#include "DSP28x_Project.h" // Device Headerfile and Examples Include File

#define TXCOUNT 1000 // Transmission will take place (TXCOUNT) times..

long i;

int j;

long loopcount = 0;

void mailbox_check(int32 T1, int32 T2, int32 T3);

void mailbox_read(int16 i);

// Global variable for this example

Uint32 ErrorCount;

Uint32 PassCount;

Uint32 MessageReceivedCount;

Uint32 TestMbox1 = 0;

Uint32 TestMbox2 = 0;

Uint32 TestMbox3 = 0;

void main(void)

{

Uint16 j;

// eCAN control registers require read/write access using 32-bits. Thus we

// will create a set of shadow registers for this example. These shadow

// registers will be used to make sure the access is 32-bits and not 16.

struct ECAN_REGS ECanaShadow;

// Step 1. Initialize System Control:

// PLL, WatchDog, enable Peripheral Clocks

// This example function is found in the DSP2833x_SysCtrl.c file.

InitSysCtrl();

// Step 2. Initalize GPIO:

// This example function is found in the DSP2833x_Gpio.c file and

// illustrates how to set the GPIO to it's default state.

// InitGpio(); // Skipped for this example

// For this example, configure CAN pins using GPIO regs here

// This function is found in DSP2833x_ECan.c

InitECanGpio();

// Step 3. Clear all interrupts and initialize PIE vector table:

// Disable CPU interrupts

DINT;

// Initialize PIE control registers to their default state.

// The default state is all PIE interrupts disabled and flags

// are cleared.

// This function is found in the DSP2833x_PieCtrl.c file.

InitPieCtrl();

// Disable CPU interrupts and clear all CPU interrupt flags:

IER = 0x0000;

IFR = 0x0000;

// Initialize the PIE vector table with pointers to the shell Interrupt

// Service Routines (ISR).

// This will populate the entire table, even if the interrupt

// is not used in this example. This is useful for debug purposes.

// The shell ISR routines are found in DSP2833x_DefaultIsr.c.

// This function is found in DSP2833x_PieVect.c.

InitPieVectTable();

// Step 4. Initialize all the Device Peripherals:

// This function is found in DSP2833x_InitPeripherals.c

// InitPeripherals(); // Not required for this example

// Step 5. User specific code, enable interrupts:

MessageReceivedCount = 0;

ErrorCount = 0;

PassCount = 0;

InitECana(); // Initialize eCAN-A module

// Mailboxs can be written to 16-bits or 32-bits at a time

// Write to the MSGID field of TRANSMIT mailboxes MBOX0 - 15

ECanaMboxes.MBOX0.MSGID.all = 0x9555AAA0;

ECanaMboxes.MBOX1.MSGID.all = 0x9555AAA1;

ECanaMboxes.MBOX2.MSGID.all = 0x9555AAA2;

ECanaMboxes.MBOX3.MSGID.all = 0x9555AAA3;

ECanaMboxes.MBOX4.MSGID.all = 0x9555AAA4;

ECanaMboxes.MBOX5.MSGID.all = 0x9555AAA5;

ECanaMboxes.MBOX6.MSGID.all = 0x9555AAA6;

ECanaMboxes.MBOX7.MSGID.all = 0x9555AAA7;

ECanaMboxes.MBOX8.MSGID.all = 0x9555AAA8;

ECanaMboxes.MBOX9.MSGID.all = 0x9555AAA9;

ECanaMboxes.MBOX10.MSGID.all = 0x9555AAAA;

ECanaMboxes.MBOX11.MSGID.all = 0x9555AAAB;

ECanaMboxes.MBOX12.MSGID.all = 0x9555AAAC;

ECanaMboxes.MBOX13.MSGID.all = 0x9555AAAD;

ECanaMboxes.MBOX14.MSGID.all = 0x9555AAAE;

ECanaMboxes.MBOX15.MSGID.all = 0x9555AAAF;

// Write to the MSGID field of RECEIVE mailboxes MBOX16 - 31

ECanaMboxes.MBOX16.MSGID.all = 0x9555AAA0;

ECanaMboxes.MBOX17.MSGID.all = 0x9555AAA1;

ECanaMboxes.MBOX18.MSGID.all = 0x9555AAA2;

ECanaMboxes.MBOX19.MSGID.all = 0x9555AAA3;

ECanaMboxes.MBOX20.MSGID.all = 0x9555AAA4;

ECanaMboxes.MBOX21.MSGID.all = 0x9555AAA5;

ECanaMboxes.MBOX22.MSGID.all = 0x9555AAA6;

ECanaMboxes.MBOX23.MSGID.all = 0x9555AAA7;

ECanaMboxes.MBOX24.MSGID.all = 0x9555AAA8;

ECanaMboxes.MBOX25.MSGID.all = 0x9555AAA9;

ECanaMboxes.MBOX26.MSGID.all = 0x9555AAAA;

ECanaMboxes.MBOX27.MSGID.all = 0x9555AAAB;

ECanaMboxes.MBOX28.MSGID.all = 0x9555AAAC;

ECanaMboxes.MBOX29.MSGID.all = 0x9555AAAD;

ECanaMboxes.MBOX30.MSGID.all = 0x9555AAAE;

ECanaMboxes.MBOX31.MSGID.all = 0x9555AAAF;

ECanaMboxes.MBOX16.MDL.all = 0;

ECanaMboxes.MBOX16.MDH.all = 0;

ECanaMboxes.MBOX17.MDL.all = 0;

ECanaMboxes.MBOX17.MDH.all = 0;

ECanaMboxes.MBOX18.MDL.all = 0;

ECanaMboxes.MBOX18.MDH.all = 0;

ECanaMboxes.MBOX19.MDL.all = 0;

ECanaMboxes.MBOX19.MDH.all = 0;

ECanaMboxes.MBOX20.MDL.all = 0;

ECanaMboxes.MBOX20.MDH.all = 0;

ECanaMboxes.MBOX21.MDL.all = 0;

ECanaMboxes.MBOX21.MDH.all = 0;

ECanaMboxes.MBOX22.MDL.all = 0;

ECanaMboxes.MBOX22.MDH.all = 0;

ECanaMboxes.MBOX23.MDL.all = 0;

ECanaMboxes.MBOX23.MDH.all = 0;

ECanaMboxes.MBOX24.MDL.all = 0;

ECanaMboxes.MBOX24.MDH.all = 0;

ECanaMboxes.MBOX25.MDL.all = 0;

ECanaMboxes.MBOX25.MDH.all = 0;

ECanaMboxes.MBOX26.MDL.all = 0;

ECanaMboxes.MBOX26.MDH.all = 0;

ECanaMboxes.MBOX27.MDL.all = 0;

ECanaMboxes.MBOX27.MDH.all = 0;

ECanaMboxes.MBOX28.MDL.all = 0;

ECanaMboxes.MBOX28.MDH.all = 0;

ECanaMboxes.MBOX29.MDL.all = 0;

ECanaMboxes.MBOX29.MDH.all = 0;

ECanaMboxes.MBOX30.MDL.all = 0;

ECanaMboxes.MBOX30.MDH.all = 0;

ECanaMboxes.MBOX31.MDL.all = 0;

ECanaMboxes.MBOX31.MDH.all = 0;

// Configure Mailboxes 0-15 as Tx, 16-31 as Rx

// Since this write is to the entire register (instead of a bit

// field) a shadow register is not required.

ECanaRegs.CANMD.all = 0xFFFF0000;

// Enable all Mailboxes */

// Since this write is to the entire register (instead of a bit

// field) a shadow register is not required.

ECanaRegs.CANME.all = 0xFFFFFFFF;

// Specify that 8 bits will be sent/received

ECanaMboxes.MBOX0.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX1.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX2.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX3.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX4.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX5.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX6.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX7.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX8.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX9.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX10.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX11.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX12.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX13.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX14.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX15.MSGCTRL.bit.DLC = 8;

// Write to the mailbox RAM field of MBOX0 - 15

ECanaMboxes.MBOX0.MDL.all = 0x9555AAA0;

ECanaMboxes.MBOX0.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX1.MDL.all = 0x9555AAA1;

ECanaMboxes.MBOX1.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX2.MDL.all = 0x9555AAA2;

ECanaMboxes.MBOX2.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX3.MDL.all = 0x9555AAA3;

ECanaMboxes.MBOX3.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX4.MDL.all = 0x9555AAA4;

ECanaMboxes.MBOX4.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX5.MDL.all = 0x9555AAA5;

ECanaMboxes.MBOX5.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX6.MDL.all = 0x9555AAA6;

ECanaMboxes.MBOX6.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX7.MDL.all = 0x9555AAA7;

ECanaMboxes.MBOX7.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX8.MDL.all = 0x9555AAA8;

ECanaMboxes.MBOX8.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX9.MDL.all = 0x9555AAA9;

ECanaMboxes.MBOX9.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX10.MDL.all = 0x9555AAAA;

ECanaMboxes.MBOX10.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX11.MDL.all = 0x9555AAAB;

ECanaMboxes.MBOX11.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX12.MDL.all = 0x9555AAAC;

ECanaMboxes.MBOX12.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX13.MDL.all = 0x9555AAAD;

ECanaMboxes.MBOX13.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX14.MDL.all = 0x9555AAAE;

ECanaMboxes.MBOX14.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX15.MDL.all = 0x9555AAAF;

ECanaMboxes.MBOX15.MDH.all = 0x89ABCDEF;

// Since this write is to the entire register (instead of a bit

// field) a shadow register is not required.

EALLOW;

ECanaRegs.CANMIM.all = 0xFFFFFFFF;

// Configure the eCAN for self test mode

// Enable the enhanced features of the eCAN.

EALLOW;

ECanaShadow.CANMC.all = ECanaRegs.CANMC.all;

ECanaShadow.CANMC.bit.STM = 0; // Configure CAN for self-test mode

ECanaRegs.CANMC.all = ECanaShadow.CANMC.all;

EDIS;

// Begin transmitting

for(i=0; i < TXCOUNT; i++)

{

ECanaRegs.CANTA.all = 0xFFFFFFFF;

ECanaRegs.CANTRS.all = 0x0000FFFF; // Set TRS for all transmit mailboxes

while(ECanaRegs.CANTA.all != 0x0000FFFF ) {} // Wait for all TAn bits to be set..

ECanaRegs.CANTA.all = 0x0000FFFF; // Clear all TAn

loopcount++;

MessageReceivedCount++;

//Read from Receive mailboxes and begin checking for data */

for(j=0; j<16; j++) // Read & check 16 mailboxes

{

mailbox_read(j); // This func reads the indicated mailbox data

mailbox_check(TestMbox1,TestMbox2,TestMbox3); // Checks the received data

}

}

}

// This function reads out the contents of the indicated

// by the Mailbox number (MBXnbr).

void mailbox_read(int16 MBXnbr)

{

volatile struct MBOX *Mailbox;

Mailbox = &ECanaMboxes.MBOX0 + MBXnbr;

TestMbox1 = Mailbox->MDL.all; // = 0x9555AAAn (n is the MBX number)

TestMbox2 = Mailbox->MDH.all; // = 0x89ABCDEF (a constant)

TestMbox3 = Mailbox->MSGID.all;// = 0x9555AAAn (n is the MBX number)

} // MSGID of a rcv MBX is transmitted as the MDL data.

void mailbox_check(int32 T1, int32 T2, int32 T3)

{

if((T1 != T3) || ( T2 != 0x89ABCDEF))

{

ErrorCount++;

}

else

{

PassCount++;

}

}

//===========================================================================

// No more.

//===========================================================================

works good.Here ,STM =1 for loopback testing

2. When STM=0 I try testing in normal mode.I get waveforms like the earlier one for sometime and then they disappear.For this I thought might be because of TxCount,but no as loopcount is not incrementing.

Even on terminating the program and starting I observe nothing.I have to wait for some time to start the program again.

Same happens with following xmit program:

// TI File $Revision: /main/2 $

// Checkin $Date: July 30, 2009 18:44:22 $

//###########################################################################

// Filename: Example_28xEcan_A_to_B_Xmit.c

//

// Description: eCAN-A To eCAN-B TXLOOP - Transmit loop

//

// ASSUMPTIONS:

//

// This program requires the DSP2833x header files.

//

// Both CAN ports of the 2833x DSP need to be connected

// to each other (via CAN transceivers)0

//

// eCANA is on GPIO31 (CANTXA) and

// GPIO30 (CANRXA)

//

// eCANB is on GPIO8 (CANTXB) and

// GPIO10 (CANRXB)

//

// As supplied, this project is configured for "boot to SARAM"

// operation. The 2833x Boot Mode table is shown below.

// For information on configuring the boot mode of an eZdsp,

// please refer to the documentation included with the eZdsp,

//

// $Boot_Table:

//

// GPIO87 GPIO86 GPIO85 GPIO84

// XA15 XA14 XA13 XA12

// PU PU PU PU

// ==========================================

// 1 1 1 1 Jump to Flash

// 1 1 1 0 SCI-A boot

// 1 1 0 1 SPI-A boot

// 1 1 0 0 I2C-A boot

// 1 0 1 1 eCAN-A boot

// 1 0 1 0 McBSP-A boot

// 1 0 0 1 Jump to XINTF x16

// 1 0 0 0 Jump to XINTF x32

// 0 1 1 1 Jump to OTP

// 0 1 1 0 Parallel GPIO I/O boot

// 0 1 0 1 Parallel XINTF boot

// 0 1 0 0 Jump to SARAM <- "boot to SARAM"

// 0 0 1 1 Branch to check boot mode

// 0 0 1 0 Boot to flash, bypass ADC cal

// 0 0 0 1 Boot to SARAM, bypass ADC cal

// 0 0 0 0 Boot to SCI-A, bypass ADC cal

// Boot_Table_End$

//

// DESCRIPTION:

//

// This example TRANSMITS data to another CAN module using MAILBOX5

// This program could either loop forever or transmit "n" # of times,

// where "n" is the TXCOUNT value.

//

// This example can be used to check CAN-A and CAN-B. Since CAN-B is

// initialized in DSP2833x_ECan.c, it will acknowledge all frames

// transmitted by the node on which this code runs. Both CAN ports of

// the 2833x DSP need to be connected to each other (via CAN transceivers)

//

//###########################################################################

// Original Author: HJ

//

// $TI Release: 2833x/2823x Header Files V1.32 $

// $Release Date: June 28, 2010 $

//###########################################################################

#include "DSP28x_Project.h" // Device Headerfile and Examples Include File

#define TXCOUNT 100 // Transmission will take place (TXCOUNT) times..

// Globals for this example

long i;

long loopcount = 0;

int b;

void main()

{

/* Create a shadow register structure for the CAN control registers. This is

needed, since, only 32-bit access is allowed to these registers. 16-bit access

to these registers could potentially corrupt the register contents. This is

especially true while writing to a bit (or group of bits) among bits 16 - 31 */

struct ECAN_REGS ECanaShadow;

// Step 1. Initialize System Control:

// PLL, WatchDog, enable Peripheral Clocks

// This example function is found in the DSP2833x_SysCtrl.c file.

InitSysCtrl();

// Step 2. Initalize GPIO:

// This example function is found in the DSP2833x_Gpio.c file and

// illustrates how to set the GPIO to it's default state.

// InitGpio(); // Skipped for this example

// Just initalize eCAN pins for this example

// This function is in DSP2833x_ECan.c

InitECanGpio();

// Step 3. Clear all interrupts and initialize PIE vector table:

// Disable CPU interrupts

DINT;

EINT;

// Initialize the PIE control registers to their default state.

// The default state is all PIE interrupts disabled and flags

// are cleared.

// This function is found in the DSP2833x_PieCtrl.c file.

InitPieCtrl();

// Disable CPU interrupts and clear all CPU interrupt flags:

IER = 0x0000;

IFR = 0x0000;

// Initialize the PIE vector table with pointers to the shell Interrupt

// Service Routines (ISR).

// This will populate the entire table, even if the interrupt

// is not used in this example. This is useful for debug purposes.

// The shell ISR routines are found in DSP2833x_DefaultIsr.c.

// This function is found in DSP2833x_PieVect.c.

InitPieVectTable();

// Interrupts that are used in this example are re-mapped to

// ISR functions found within this file.

// No interrupts used in this example.

// Step 4. Initialize all the Device Peripherals:

// This function is found in DSP2833x_InitPeripherals.c

// InitPeripherals(); // Not required for this example

// In this case just initalize eCAN-A and eCAN-B

// This function is in DSP2833x_ECan.c

InitECan();

// Step 5. User specific code:

/* Write to the MSGID field */

ECanaMboxes.MBOX25.MSGID.all = 0x95555555; // Extended Identifier

/* Configure Mailbox under test as a Transmit mailbox */

ECanaShadow.CANMD.all = ECanaRegs.CANMD.all;

ECanaShadow.CANMD.bit.MD25 = 0;

ECanaRegs.CANMD.all = ECanaShadow.CANMD.all;

/* Enable Mailbox under test */

ECanaShadow.CANME.all = ECanaRegs.CANME.all;

ECanaShadow.CANME.bit.ME25 = 1;

ECanaRegs.CANME.all = ECanaShadow.CANME.all;

/* Write to DLC field in Master Control reg */

ECanaMboxes.MBOX25.MSGCTRL.bit.DLC = 8;

/* Write to the mailbox RAM field */

ECanaMboxes.MBOX25.MDL.all = 0x55555555;

ECanaMboxes.MBOX25.MDH.all = 0x55555555;

/* Begin transmitting */

b=0;

for(;;)

{

b=1;

ECanaShadow.CANTRS.all = 0;

ECanaShadow.CANTRS.bit.TRS25 = 1; // Set TRS for mailbox under test

ECanaRegs.CANTRS.all = ECanaShadow.CANTRS.all;

b=2;

do

{

ECanaShadow.CANTA.all = ECanaRegs.CANTA.all;

} while(ECanaShadow.CANTA.bit.TA25 == 0 ); // Wait for TA5 bit to be set..

b=3;

ECanaShadow.CANTA.all = 0;

ECanaShadow.CANTA.bit.TA25 = 1; // Clear TA5

ECanaRegs.CANTA.all = ECanaShadow.CANTA.all;

b=4;

loopcount ++;

}

asm(" ESTOP0"); // Stop here

}

I am definitely wrong somewhere in hardware guess.

Thanks

Sneha

HI Sunil

One more thing,I have tested my hardware setup by giving 100kHz pulses from GPIO 31 to CAN transciever TXD pin and i get correct CANH/CANL waveforms;

I get this any no of times I try,whether I halt /terminate the program.

With the same setup, only diff now is I give CAN Tx output to TXD of transciever and I get nothing..a lil glimpse of waveforms which I ma getting is really not noticeable.

Thanks

Sneha

Hi Sunil

I am trying to run control suite example program eCAN A-B xmit:

// TI File $Revision: /main/2 $

// Checkin $Date: July 30, 2009 18:44:22 $

//###########################################################################

// Filename: Example_28xEcan_A_to_B_Xmit.c

//

// Description: eCAN-A To eCAN-B TXLOOP - Transmit loop

//

// ASSUMPTIONS:

//

// This program requires the DSP2833x header files.

//

// Both CAN ports of the 2833x DSP need to be connected

// to each other (via CAN transceivers)0

//

// eCANA is on GPIO31 (CANTXA) and

// GPIO30 (CANRXA)

//

// eCANB is on GPIO8 (CANTXB) and

// GPIO10 (CANRXB)

//

// As supplied, this project is configured for "boot to SARAM"

// operation. The 2833x Boot Mode table is shown below.

// For information on configuring the boot mode of an eZdsp,

// please refer to the documentation included with the eZdsp,

//

// $Boot_Table:

//

// GPIO87 GPIO86 GPIO85 GPIO84

// XA15 XA14 XA13 XA12

// PU PU PU PU

// ==========================================

// 1 1 1 1 Jump to Flash

// 1 1 1 0 SCI-A boot

// 1 1 0 1 SPI-A boot

// 1 1 0 0 I2C-A boot

// 1 0 1 1 eCAN-A boot

// 1 0 1 0 McBSP-A boot

// 1 0 0 1 Jump to XINTF x16

// 1 0 0 0 Jump to XINTF x32

// 0 1 1 1 Jump to OTP

// 0 1 1 0 Parallel GPIO I/O boot

// 0 1 0 1 Parallel XINTF boot

// 0 1 0 0 Jump to SARAM <- "boot to SARAM"

// 0 0 1 1 Branch to check boot mode

// 0 0 1 0 Boot to flash, bypass ADC cal

// 0 0 0 1 Boot to SARAM, bypass ADC cal

// 0 0 0 0 Boot to SCI-A, bypass ADC cal

// Boot_Table_End$

//

// DESCRIPTION:

//

// This example TRANSMITS data to another CAN module using MAILBOX5

// This program could either loop forever or transmit "n" # of times,

// where "n" is the TXCOUNT value.

//

// This example can be used to check CAN-A and CAN-B. Since CAN-B is

// initialized in DSP2833x_ECan.c, it will acknowledge all frames

// transmitted by the node on which this code runs. Both CAN ports of

// the 2833x DSP need to be connected to each other (via CAN transceivers)

//

//###########################################################################

// Original Author: HJ

//

// $TI Release: 2833x/2823x Header Files V1.32 $

// $Release Date: June 28, 2010 $

//###########################################################################

#include "DSP28x_Project.h" // Device Headerfile and Examples Include File

#define TXCOUNT 100 // Transmission will take place (TXCOUNT) times..

// Globals for this example

long i;

long loopcount = 0;

void main()

{

/* Create a shadow register structure for the CAN control registers. This is

needed, since, only 32-bit access is allowed to these registers. 16-bit access

to these registers could potentially corrupt the register contents. This is

especially true while writing to a bit (or group of bits) among bits 16 - 31 */

struct ECAN_REGS ECanaShadow;

// Step 1. Initialize System Control:

// PLL, WatchDog, enable Peripheral Clocks

// This example function is found in the DSP2833x_SysCtrl.c file.

InitSysCtrl();

// Step 2. Initalize GPIO:

// This example function is found in the DSP2833x_Gpio.c file and

// illustrates how to set the GPIO to it's default state.

// InitGpio(); // Skipped for this example

// Just initalize eCAN pins for this example

// This function is in DSP2833x_ECan.c

InitECanGpio();

// Step 3. Clear all interrupts and initialize PIE vector table:

// Disable CPU interrupts

DINT;

// Initialize the PIE control registers to their default state.

// The default state is all PIE interrupts disabled and flags

// are cleared.

// This function is found in the DSP2833x_PieCtrl.c file.

InitPieCtrl();

// Disable CPU interrupts and clear all CPU interrupt flags:

IER = 0x0000;

IFR = 0x0000;

// Initialize the PIE vector table with pointers to the shell Interrupt

// Service Routines (ISR).

// This will populate the entire table, even if the interrupt

// is not used in this example. This is useful for debug purposes.

// The shell ISR routines are found in DSP2833x_DefaultIsr.c.

// This function is found in DSP2833x_PieVect.c.

InitPieVectTable();

// Interrupts that are used in this example are re-mapped to

// ISR functions found within this file.

// No interrupts used in this example.

// Step 4. Initialize all the Device Peripherals:

// This function is found in DSP2833x_InitPeripherals.c

// InitPeripherals(); // Not required for this example

// In this case just initalize eCAN-A and eCAN-B

// This function is in DSP2833x_ECan.c

InitECan();

// Step 5. User specific code:

/* Write to the MSGID field */

ECanaMboxes.MBOX25.MSGID.all = 0x95555555; // Extended Identifier

/* Configure Mailbox under test as a Transmit mailbox */

ECanaShadow.CANMD.all = ECanaRegs.CANMD.all;

ECanaShadow.CANMD.bit.MD25 = 0;

ECanaRegs.CANMD.all = ECanaShadow.CANMD.all;

/* Enable Mailbox under test */

ECanaShadow.CANME.all = ECanaRegs.CANME.all;

ECanaShadow.CANME.bit.ME25 = 1;

ECanaRegs.CANME.all = ECanaShadow.CANME.all;

/* Write to DLC field in Master Control reg */

ECanaMboxes.MBOX25.MSGCTRL.bit.DLC = 8;

/* Write to the mailbox RAM field */

ECanaMboxes.MBOX25.MDL.all = 0x55555555;

ECanaMboxes.MBOX25.MDH.all = 0x55555555;

/* Begin transmitting */

for(i=0; i < TXCOUNT; i++)

{

ECanaShadow.CANTRS.all = 0;

ECanaShadow.CANTRS.bit.TRS25 = 1; // Set TRS for mailbox under test

ECanaRegs.CANTRS.all = ECanaShadow.CANTRS.all;

do

{

ECanaShadow.CANTA.all = ECanaRegs.CANTA.all;

} while(ECanaShadow.CANTA.bit.TA25 == 0 ); // Wait for TA5 bit to be set..

ECanaShadow.CANTA.all = 0;

ECanaShadow.CANTA.bit.TA25 = 1; // Clear TA5

ECanaRegs.CANTA.all = ECanaShadow.CANTA.all;

loopcount ++;

}

asm(" ESTOP0"); // Stop here

}

In this If I connect tx-rx full connection I dont observe anything with CAN-B registers.Therefore,I am trying to Observe CANH nCANL waveforms first,to enxure if really there is some data.But I do not get the bus.It comes for sometime,the problem.

I tried writing the following program for TX and RX in CAN but I did not recieve anything on CAN-2 registers,Nor I got any CAN bus.

// TI File $Revision: /main/2 $

// Checkin $Date: July 30, 2009 18:44:22 $

//###########################################################################

// Filename: Example_28xEcan_A_to_B_Xmit.c

//

// Description: eCANA-1 to eCANA2 Transmit loop

//

// ASSUMPTIONS:

//

// This program requires the DSP2833x header files.

//

// The CAN ports A of the two 2833x DSP need to be connected

// to each other (via CAN transceivers)0

//

// Transmitter end- eCANA1 is on GPIO19 (CANTXA) and

// GPIO18 (CANRXA)

//

// Reciever end- eCANA2 is on GPIO19 (CANTXB) and

// GPIO18 (CANRXB)

//

// As supplied, this project is configured for "boot to SARAM"

// operation. The 2833x Boot Mode table is shown below.

// For information on configuring the boot mode of an eZdsp,

// please refer to the documentation included with the eZdsp,

//

// $Boot_Table:

//

// GPIO87 GPIO86 GPIO85 GPIO84

// XA15 XA14 XA13 XA12

// PU PU PU PU

// ==========================================

// 1 1 1 1 Jump to Flash

// 1 1 1 0 SCI-A boot

// 1 1 0 1 SPI-A boot

// 1 1 0 0 I2C-A boot

// 1 0 1 1 eCAN-A boot

// 1 0 1 0 McBSP-A boot

// 1 0 0 1 Jump to XINTF x16

// 1 0 0 0 Jump to XINTF x32

// 0 1 1 1 Jump to OTP

// 0 1 1 0 Parallel GPIO I/O boot

// 0 1 0 1 Parallel XINTF boot

// 0 1 0 0 Jump to SARAM <- "boot to SARAM"

// 0 0 1 1 Branch to check boot mode

// 0 0 1 0 Boot to flash, bypass ADC cal

// 0 0 0 1 Boot to SARAM, bypass ADC cal

// 0 0 0 0 Boot to SCI-A, bypass ADC cal

// Boot_Table_End$

//

// DESCRIPTION:

//

// This example TRANSMITS data from MAILBOX5, CANA on DSP1 to another DS2P CANA module MAILBOX1

// This program could either loop forever or transmit "n" # of times,

// where "n" is the TXCOUNT value.

//

// ###########################################################################

#include "DSP28x_Project.h"

// Prototype statements for functions found within this file.

Uint16 loopcount =0;

// Global Variables

/* Create a shadow register structure for the CAN control registers. This is

needed, since, only 32-bit access is allowed to these registers. 16-bit access

to these registers could potentially corrupt the register contents. This is

especially true while writing to a bit (or group of bits) among bits 16 - 31 */

struct ECAN_REGS ECanaShadow;

main()

{

// Initialize System Control registers, PLL, WatchDog, Clocks to default state:

// This function is found in the DSP28_SysCtrl.c file.

InitSysCtrl();

// Initialise the physical pins of the DSP

//* Initialize the CAN module */

InitECan();

/* Write to the MSGID field */

ECanaMboxes.MBOX5.MSGID.all = 0x11111111;

ECanaMboxes.MBOX5.MSGID.bit.IDE = 1; // Extended Identifier

/* Configure Mailbox under test as a Transmit mailbox */

ECanaShadow.CANMD.all = ECanaRegs.CANMD.all;

ECanaShadow.CANMD.bit.MD5 = 0;

ECanaRegs.CANMD.all = ECanaShadow.CANMD.all;

/* Enable Mailbox under test */

ECanaShadow.CANME.all = ECanaRegs.CANME.all;

ECanaShadow.CANME.bit.ME5 = 1;

ECanaRegs.CANME.all = ECanaShadow.CANME.all;

/* Write to DLC field in Master Control reg */

ECanaMboxes.MBOX5.MSGCTRL.bit.DLC = 1;

ECanaMboxes.MBOX5.MDL.all = 0x00000005;

ECanaMboxes.MBOX5.MDH.all = 0x00000005;

/* Begin transmitting */

for(;;)

{

ECanaShadow.CANTRS.all = 0;

ECanaShadow.CANTRS.bit.TRS5 = 1; // Set TRS for mailbox under test

ECanaRegs.CANTRS.all = ECanaShadow.CANTRS.all;

do

{

ECanaShadow.CANTA.all = ECanaRegs.CANTA.all;

} while(ECanaShadow.CANTA.bit.TA5 == 0 ); // Wait for TA5 bit to be set..

ECanaShadow.CANTA.all = 0;

ECanaShadow.CANTA.bit.TA5 = 1; // Clear TA5

ECanaRegs.CANTA.all = ECanaShadow.CANTA.all;

loopcount ++;

}

asm(" ESTOP0"); // Stop here

}

// TI File $Revision: /main/2 $

// Checkin $Date: July 30, 2009 18:44:22 $

//###########################################################################

// Filename: Example_28xEcan_A_to_B_Xmit.c

//

// Description: eCANA-1 to eCANA2 Transmit loop

//

// ASSUMPTIONS:

//

// This program requires the DSP2833x header files.

//

// The CAN ports A of the two 2833x DSP need to be connected

// to each other (via CAN transceivers)0

//

// Transmitter end- eCANA1 is on GPIO19 (CANTXA) and

// GPIO18 (CANRXA)

//

// Reciever end- eCANA2 is on GPIO19 (CANTXB) and

// GPIO18 (CANRXB)

//

// As supplied, this project is configured for "boot to SARAM"

// operation. The 2833x Boot Mode table is shown below.

// For information on configuring the boot mode of an eZdsp,

// please refer to the documentation included with the eZdsp,

//

// $Boot_Table:

//

// GPIO87 GPIO86 GPIO85 GPIO84

// XA15 XA14 XA13 XA12

// PU PU PU PU

// ==========================================

// 1 1 1 1 Jump to Flash

// 1 1 1 0 SCI-A boot

// 1 1 0 1 SPI-A boot

// 1 1 0 0 I2C-A boot

// 1 0 1 1 eCAN-A boot

// 1 0 1 0 McBSP-A boot

// 1 0 0 1 Jump to XINTF x16

// 1 0 0 0 Jump to XINTF x32

// 0 1 1 1 Jump to OTP

// 0 1 1 0 Parallel GPIO I/O boot

// 0 1 0 1 Parallel XINTF boot

// 0 1 0 0 Jump to SARAM <- "boot to SARAM"

// 0 0 1 1 Branch to check boot mode

// 0 0 1 0 Boot to flash, bypass ADC cal

// 0 0 0 1 Boot to SARAM, bypass ADC cal

// 0 0 0 0 Boot to SCI-A, bypass ADC cal

// Boot_Table_End$

//

// DESCRIPTION:

//

// This example TRANSMITS data from MAILBOX5, CANA on DSP1 to another DS2P CANA module MAILBOX1

// This program could either loop forever or transmit "n" # of times,

// where "n" is the TXCOUNT value.

//

// ###########################################################################

#include "DSP28x_Project.h"

// Prototype statements for functions found within this file.

// Global Variables

/* Create a shadow register structure for the CAN control registers. This is

needed, since, only 32-bit access is allowed to these registers. 16-bit access

to these registers could potentially corrupt the register contents. This is

especially true while writing to a bit (or group of bits) among bits 16 - 31 */

struct ECAN_REGS ECanaShadow;

main()

{

// Initialize System Control registers, PLL, WatchDog, Clocks to default state:

// This function is found in the DSP28_SysCtrl.c file.

InitSysCtrl();

// Initialise the physical pins of the DSP

//* Initialize the CAN module */

InitECan();

/* Write to the MSGID field - MBX number is written as its MSGID */

ECanaMboxes.MBOX1.MSGID.all = 0x11111111; // extended identifier

ECanaMboxes.MBOX1.MSGID.bit.IDE = 1;

/* Configure Mailbox 1 as Receiver mailbox */

ECanaShadow.CANMD.all = ECanaRegs.CANMD.all;

ECanaShadow.CANMD.bit.MD1 = 1;

ECanaRegs.CANMD.all = ECanaShadow.CANMD.all;

ECanaMboxes.MBOX1.MSGCTRL.all = 0;

ECanaMboxes.MBOX1.MSGCTRL.bit.DLC = 2;

/* Enable Mailbox 1 */

ECanaShadow.CANME.all = ECanaRegs.CANME.all;

ECanaShadow.CANME.bit.ME1 = 1;

ECanaRegs.CANME.all = ECanaShadow.CANME.all;

/* Begin Receiving */

while(1)

{

do {

ECanaShadow.CANRMP.all = ECanaRegs.CANRMP.all;

}

while(ECanaShadow.CANRMP.bit.RMP1 != 1 ); // Wait for RMP1 to be set..

ECanaShadow.CANRMP.bit.RMP1 = 1;

ECanaRegs.CANRMP.all = ECanaShadow.CANRMP.all; // Clear RMP1 bit and start again

}

}

HI SUnil

Also,as suggested by you I am running the following loopback program for eCAN with STM=1for self test mode,which works great...

but with STM =0 nothing...

// TI File $Revision: /main/2 $

// Checkin $Date: July 30, 2009 18:44:23 $

//###########################################################################

//

// FILE: Example_2833xECanBack2Back.c

//

// TITLE: DSP2833x eCAN Back-to-back transmission and reception in

// SELF-TEST mode

//

// ASSUMPTIONS:

//

// This program requires the DSP2833x header files.

//

// This progrm uses the peripheral's self test mode.

// Other then boot mode configuration, no other hardware configuration

// is required.

//

// As supplied, this project is configured for "boot to SARAM"

// operation. The 2833x Boot Mode table is shown below.

// For information on configuring the boot mode of an eZdsp,

// please refer to the documentation included with the eZdsp,

//

// $Boot_Table:

//

// GPIO87 GPIO86 GPIO85 GPIO84

// XA15 XA14 XA13 XA12

// PU PU PU PU

// ==========================================

// 1 1 1 1 Jump to Flash

// 1 1 1 0 SCI-A boot

// 1 1 0 1 SPI-A boot

// 1 1 0 0 I2C-A boot

// 1 0 1 1 eCAN-A boot

// 1 0 1 0 McBSP-A boot

// 1 0 0 1 Jump to XINTF x16

// 1 0 0 0 Jump to XINTF x32

// 0 1 1 1 Jump to OTP

// 0 1 1 0 Parallel GPIO I/O boot

// 0 1 0 1 Parallel XINTF boot

// 0 1 0 0 Jump to SARAM <- "boot to SARAM"

// 0 0 1 1 Branch to check boot mode

// 0 0 1 0 Boot to flash, bypass ADC cal

// 0 0 0 1 Boot to SARAM, bypass ADC cal

// 0 0 0 0 Boot to SCI-A, bypass ADC cal

// Boot_Table_End$

//

// DESCRIPTION:

//

// This test transmits data back-to-back at high speed without

// stopping.

// The received data is verified. Any error is flagged.

// MBX0 transmits to MBX16, MBX1 transmits to MBX17 and so on....

// This program illustrates the use of self-test mode

//

//###########################################################################

// Original Author H.J.

//

// $TI Release: 2833x/2823x Header Files V1.32 $

// $Release Date: June 28, 2010 $

//###########################################################################

#include "DSP28x_Project.h" // Device Headerfile and Examples Include File

#define TXCOUNT 1000 // Transmission will take place (TXCOUNT) times..

long i;

int j;

long loopcount = 0;

void mailbox_check(int32 T1, int32 T2, int32 T3);

void mailbox_read(int16 i);

// Global variable for this example

Uint32 ErrorCount;

Uint32 PassCount;

Uint32 MessageReceivedCount;

Uint32 TestMbox1 = 0;

Uint32 TestMbox2 = 0;

Uint32 TestMbox3 = 0;

void main(void)

{

Uint16 j;

// eCAN control registers require read/write access using 32-bits. Thus we

// will create a set of shadow registers for this example. These shadow

// registers will be used to make sure the access is 32-bits and not 16.

struct ECAN_REGS ECanaShadow;

// Step 1. Initialize System Control:

// PLL, WatchDog, enable Peripheral Clocks

// This example function is found in the DSP2833x_SysCtrl.c file.

InitSysCtrl();

// Step 2. Initalize GPIO:

// This example function is found in the DSP2833x_Gpio.c file and

// illustrates how to set the GPIO to it's default state.

// InitGpio(); // Skipped for this example

// For this example, configure CAN pins using GPIO regs here

// This function is found in DSP2833x_ECan.c

InitECanGpio();

// Step 3. Clear all interrupts and initialize PIE vector table:

// Disable CPU interrupts

DINT;

// Initialize PIE control registers to their default state.

// The default state is all PIE interrupts disabled and flags

// are cleared.

// This function is found in the DSP2833x_PieCtrl.c file.

InitPieCtrl();

// Disable CPU interrupts and clear all CPU interrupt flags:

IER = 0x0000;

IFR = 0x0000;

// Initialize the PIE vector table with pointers to the shell Interrupt

// Service Routines (ISR).

// This will populate the entire table, even if the interrupt

// is not used in this example. This is useful for debug purposes.

// The shell ISR routines are found in DSP2833x_DefaultIsr.c.

// This function is found in DSP2833x_PieVect.c.

InitPieVectTable();

// Step 4. Initialize all the Device Peripherals:

// This function is found in DSP2833x_InitPeripherals.c

// InitPeripherals(); // Not required for this example

// Step 5. User specific code, enable interrupts:

MessageReceivedCount = 0;

ErrorCount = 0;

PassCount = 0;

InitECana(); // Initialize eCAN-A module

// Mailboxs can be written to 16-bits or 32-bits at a time

// Write to the MSGID field of TRANSMIT mailboxes MBOX0 - 15

ECanaMboxes.MBOX0.MSGID.all = 0x9555AAA0;

ECanaMboxes.MBOX1.MSGID.all = 0x9555AAA1;

ECanaMboxes.MBOX2.MSGID.all = 0x9555AAA2;

ECanaMboxes.MBOX3.MSGID.all = 0x9555AAA3;

ECanaMboxes.MBOX4.MSGID.all = 0x9555AAA4;

ECanaMboxes.MBOX5.MSGID.all = 0x9555AAA5;

ECanaMboxes.MBOX6.MSGID.all = 0x9555AAA6;

ECanaMboxes.MBOX7.MSGID.all = 0x9555AAA7;

ECanaMboxes.MBOX8.MSGID.all = 0x9555AAA8;

ECanaMboxes.MBOX9.MSGID.all = 0x9555AAA9;

ECanaMboxes.MBOX10.MSGID.all = 0x9555AAAA;

ECanaMboxes.MBOX11.MSGID.all = 0x9555AAAB;

ECanaMboxes.MBOX12.MSGID.all = 0x9555AAAC;

ECanaMboxes.MBOX13.MSGID.all = 0x9555AAAD;

ECanaMboxes.MBOX14.MSGID.all = 0x9555AAAE;

ECanaMboxes.MBOX15.MSGID.all = 0x9555AAAF;

// Write to the MSGID field of RECEIVE mailboxes MBOX16 - 31

ECanaMboxes.MBOX16.MSGID.all = 0x9555AAA0;

ECanaMboxes.MBOX17.MSGID.all = 0x9555AAA1;

ECanaMboxes.MBOX18.MSGID.all = 0x9555AAA2;

ECanaMboxes.MBOX19.MSGID.all = 0x9555AAA3;

ECanaMboxes.MBOX20.MSGID.all = 0x9555AAA4;

ECanaMboxes.MBOX21.MSGID.all = 0x9555AAA5;

ECanaMboxes.MBOX22.MSGID.all = 0x9555AAA6;

ECanaMboxes.MBOX23.MSGID.all = 0x9555AAA7;

ECanaMboxes.MBOX24.MSGID.all = 0x9555AAA8;

ECanaMboxes.MBOX25.MSGID.all = 0x9555AAA9;

ECanaMboxes.MBOX26.MSGID.all = 0x9555AAAA;

ECanaMboxes.MBOX27.MSGID.all = 0x9555AAAB;

ECanaMboxes.MBOX28.MSGID.all = 0x9555AAAC;

ECanaMboxes.MBOX29.MSGID.all = 0x9555AAAD;

ECanaMboxes.MBOX30.MSGID.all = 0x9555AAAE;

ECanaMboxes.MBOX31.MSGID.all = 0x9555AAAF;

ECanaMboxes.MBOX16.MDL.all = 0;

ECanaMboxes.MBOX16.MDH.all = 0;

ECanaMboxes.MBOX17.MDL.all = 0;

ECanaMboxes.MBOX17.MDH.all = 0;

ECanaMboxes.MBOX18.MDL.all = 0;

ECanaMboxes.MBOX18.MDH.all = 0;

ECanaMboxes.MBOX19.MDL.all = 0;

ECanaMboxes.MBOX19.MDH.all = 0;

ECanaMboxes.MBOX20.MDL.all = 0;

ECanaMboxes.MBOX20.MDH.all = 0;

ECanaMboxes.MBOX21.MDL.all = 0;

ECanaMboxes.MBOX21.MDH.all = 0;

ECanaMboxes.MBOX22.MDL.all = 0;

ECanaMboxes.MBOX22.MDH.all = 0;

ECanaMboxes.MBOX23.MDL.all = 0;

ECanaMboxes.MBOX23.MDH.all = 0;

ECanaMboxes.MBOX24.MDL.all = 0;

ECanaMboxes.MBOX24.MDH.all = 0;

ECanaMboxes.MBOX25.MDL.all = 0;

ECanaMboxes.MBOX25.MDH.all = 0;

ECanaMboxes.MBOX26.MDL.all = 0;

ECanaMboxes.MBOX26.MDH.all = 0;

ECanaMboxes.MBOX27.MDL.all = 0;

ECanaMboxes.MBOX27.MDH.all = 0;

ECanaMboxes.MBOX28.MDL.all = 0;

ECanaMboxes.MBOX28.MDH.all = 0;

ECanaMboxes.MBOX29.MDL.all = 0;

ECanaMboxes.MBOX29.MDH.all = 0;

ECanaMboxes.MBOX30.MDL.all = 0;

ECanaMboxes.MBOX30.MDH.all = 0;

ECanaMboxes.MBOX31.MDL.all = 0;

ECanaMboxes.MBOX31.MDH.all = 0;

// Configure Mailboxes 0-15 as Tx, 16-31 as Rx

// Since this write is to the entire register (instead of a bit

// field) a shadow register is not required.

ECanaRegs.CANMD.all = 0xFFFF0000;

// Enable all Mailboxes */

// Since this write is to the entire register (instead of a bit

// field) a shadow register is not required.

ECanaRegs.CANME.all = 0xFFFFFFFF;

// Specify that 8 bits will be sent/received

ECanaMboxes.MBOX0.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX1.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX2.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX3.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX4.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX5.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX6.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX7.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX8.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX9.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX10.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX11.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX12.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX13.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX14.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX15.MSGCTRL.bit.DLC = 8;

// Write to the mailbox RAM field of MBOX0 - 15

ECanaMboxes.MBOX0.MDL.all = 0x9555AAA0;

ECanaMboxes.MBOX0.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX1.MDL.all = 0x9555AAA1;

ECanaMboxes.MBOX1.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX2.MDL.all = 0x9555AAA2;

ECanaMboxes.MBOX2.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX3.MDL.all = 0x9555AAA3;

ECanaMboxes.MBOX3.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX4.MDL.all = 0x9555AAA4;

ECanaMboxes.MBOX4.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX5.MDL.all = 0x9555AAA5;

ECanaMboxes.MBOX5.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX6.MDL.all = 0x9555AAA6;

ECanaMboxes.MBOX6.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX7.MDL.all = 0x9555AAA7;

ECanaMboxes.MBOX7.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX8.MDL.all = 0x9555AAA8;

ECanaMboxes.MBOX8.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX9.MDL.all = 0x9555AAA9;

ECanaMboxes.MBOX9.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX10.MDL.all = 0x9555AAAA;

ECanaMboxes.MBOX10.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX11.MDL.all = 0x9555AAAB;

ECanaMboxes.MBOX11.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX12.MDL.all = 0x9555AAAC;

ECanaMboxes.MBOX12.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX13.MDL.all = 0x9555AAAD;

ECanaMboxes.MBOX13.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX14.MDL.all = 0x9555AAAE;

ECanaMboxes.MBOX14.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX15.MDL.all = 0x9555AAAF;

ECanaMboxes.MBOX15.MDH.all = 0x89ABCDEF;

// Since this write is to the entire register (instead of a bit

// field) a shadow register is not required.

EALLOW;

ECanaRegs.CANMIM.all = 0xFFFFFFFF;

// Configure the eCAN for self test mode

// Enable the enhanced features of the eCAN.

EALLOW;

ECanaShadow.CANMC.all = ECanaRegs.CANMC.all;

ECanaShadow.CANMC.bit.STM = 0; // Configure CAN for self-test mode

ECanaRegs.CANMC.all = ECanaShadow.CANMC.all;

EDIS;

// Begin transmitting

for(i=0; i < TXCOUNT; i++)

{

ECanaRegs.CANTA.all = 0xFFFFFFFF;

ECanaRegs.CANTRS.all = 0x0000FFFF; // Set TRS for all transmit mailboxes

while(ECanaRegs.CANTA.all != 0x0000FFFF ) {} // Wait for all TAn bits to be set..

ECanaRegs.CANTA.all = 0x0000FFFF; // Clear all TAn

loopcount++;

MessageReceivedCount++;

//Read from Receive mailboxes and begin checking for data */

for(j=0; j<16; j++) // Read & check 16 mailboxes

{

mailbox_read(j); // This func reads the indicated mailbox data

mailbox_check(TestMbox1,TestMbox2,TestMbox3); // Checks the received data

}

}

}

// This function reads out the contents of the indicated

// by the Mailbox number (MBXnbr).

void mailbox_read(int16 MBXnbr)

{

volatile struct MBOX *Mailbox;

Mailbox = &ECanaMboxes.MBOX0 + MBXnbr;

TestMbox1 = Mailbox->MDL.all; // = 0x9555AAAn (n is the MBX number)

TestMbox2 = Mailbox->MDH.all; // = 0x89ABCDEF (a constant)

TestMbox3 = Mailbox->MSGID.all;// = 0x9555AAAn (n is the MBX number)

} // MSGID of a rcv MBX is transmitted as the MDL data.

void mailbox_check(int32 T1, int32 T2, int32 T3)

{

if((T1 != T3) || ( T2 != 0x89ABCDEF))

{

ErrorCount++;

}

else

{

PassCount++;

}

}

//===========================================================================

// No more.

//===========================================================================

Hi Sunil

I am really thankful for all your help till now.But I am still unable to sort out the issue.

I have made the changes as suggested by you in the CAN Tx and CAN Rx programs and set the bit rate at 125 kbps.

On one side I am using the CAN transciever ISO1050EVM and on the other the transciever circuit made by using ISO1050 with no terminating resistance as EVM already has 60 ohm terminating resistance.

But there is no communication and I get those continuous high waveforms only.

I am loosing my patience now.How do I identify the problem.

Hope You can suggest something.

1. can tx

// TI File $Revision: /main/2 $

// Checkin $Date: July 30, 2009 18:44:22 $

//###########################################################################

// Filename: Example_28xEcan_A_to_B_Xmit.c

//

// Description: eCANA-1 to eCANA2 Transmit loop

//

// ASSUMPTIONS:

//

// This program requires the DSP2833x header files.

//

// The CAN ports A of the two 2833x DSP need to be connected

// to each other (via CAN transceivers)0

//

// Transmitter end- eCANA1 is on GPIO19 (CANTXA) and

// GPIO18 (CANRXA)

//

// Reciever end- eCANA2 is on GPIO19 (CANTXB) and

// GPIO18 (CANRXB)

//

// As supplied, this project is configured for "boot to SARAM"

// operation. The 2833x Boot Mode table is shown below.

// For information on configuring the boot mode of an eZdsp,

// please refer to the documentation included with the eZdsp,

//

// $Boot_Table:

//

// GPIO87 GPIO86 GPIO85 GPIO84

// XA15 XA14 XA13 XA12

// PU PU PU PU

// ==========================================

// 1 1 1 1 Jump to Flash

// 1 1 1 0 SCI-A boot

// 1 1 0 1 SPI-A boot

// 1 1 0 0 I2C-A boot

// 1 0 1 1 eCAN-A boot

// 1 0 1 0 McBSP-A boot

// 1 0 0 1 Jump to XINTF x16

// 1 0 0 0 Jump to XINTF x32

// 0 1 1 1 Jump to OTP

// 0 1 1 0 Parallel GPIO I/O boot

// 0 1 0 1 Parallel XINTF boot

// 0 1 0 0 Jump to SARAM <- "boot to SARAM"

// 0 0 1 1 Branch to check boot mode

// 0 0 1 0 Boot to flash, bypass ADC cal

// 0 0 0 1 Boot to SARAM, bypass ADC cal

// 0 0 0 0 Boot to SCI-A, bypass ADC cal

// Boot_Table_End$

//

// DESCRIPTION:

//

// This example TRANSMITS data from MAILBOX5, CANA on DSP1 to another DS2P CANA module MAILBOX1

// This program could either loop forever or transmit "n" # of times,

// where "n" is the TXCOUNT value.

//

// ###########################################################################

#include "DSP28x_Project.h"

// Prototype statements for functions found within this file.

Uint16 loopcount =0;

// Global Variables

/* Create a shadow register structure for the CAN control registers. This is

needed, since, only 32-bit access is allowed to these registers. 16-bit access

to these registers could potentially corrupt the register contents. This is

especially true while writing to a bit (or group of bits) among bits 16 - 31 */

struct ECAN_REGS ECanaShadow;

main()

{

// Initialize System Control registers, PLL, WatchDog, Clocks to default state:

// This function is found in the DSP28_SysCtrl.c file.

InitSysCtrl();

// Initialise the physical pins of the DSP

//* Initialize the CAN module */

InitECan();

/* Write to the MSGID field */

ECanaMboxes.MBOX1.MSGID.all = 0x00050000;

ECanaMboxes.MBOX1.MSGID.bit.IDE = 0; // standard Identifier

/* Configure Mailbox under test as a Transmit mailbox */

ECanaShadow.CANMD.all = ECanaRegs.CANMD.all;

ECanaShadow.CANMD.bit.MD1 = 0;

ECanaRegs.CANMD.all = ECanaShadow.CANMD.all;

/* Enable Mailbox under test */

ECanaShadow.CANME.all = ECanaRegs.CANME.all;

ECanaShadow.CANME.bit.ME1 = 1;

ECanaRegs.CANME.all = ECanaShadow.CANME.all;

/* Write to DLC field in Master Control reg */

ECanaMboxes.MBOX1.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX1.MDL.all = 0x0000008A;

ECanaMboxes.MBOX1.MDH.all = 0x0000008A;

/* Begin transmitting */

for(;;)

{

ECanaShadow.CANTRS.all = 0;

ECanaShadow.CANTRS.bit.TRS1 = 1; // Set TRS for mailbox under test

ECanaRegs.CANTRS.all = ECanaShadow.CANTRS.all;

do

{

ECanaShadow.CANTA.all = ECanaRegs.CANTA.all;

} while(ECanaShadow.CANTA.bit.TA1 == 0 ); // Wait for TA5 bit to be set..

ECanaShadow.CANTA.all = 0;

ECanaShadow.CANTA.bit.TA1 = 1; // Clear TA5

ECanaRegs.CANTA.all = ECanaShadow.CANTA.all;

loopcount ++;

}

asm(" ESTOP0"); // Stop here

}

2. can TX .C

// TI File $Revision: /main/8 $

// Checkin $Date: June 25, 2008 15:19:07 $

//###########################################################################

//

// FILE: DSP2833x_ECan.c

//

// TITLE: DSP2833x Enhanced CAN Initialization & Support Functions.

//

//###########################################################################

// $TI Release: 2833x/2823x Header Files V1.32 $

// $Release Date: June 28, 2010 $

//###########################################################################

#include "DSP2833x_Device.h" // DSP2833x Headerfile Include File

#include "DSP2833x_Examples.h" // DSP2833x Examples Include File

//---------------------------------------------------------------------------

// InitECan:

//---------------------------------------------------------------------------

// This function initializes the eCAN module to a known state.

//

void InitECan(void)

{

InitECana();

#if DSP28_ECANB

InitECanb();

#endif // if DSP28_ECANB

}

void InitECana(void) // Initialize eCAN-A module

{

/* Create a shadow register structure for the CAN control registers. This is

needed, since only 32-bit access is allowed to these registers. 16-bit access

to these registers could potentially corrupt the register contents or return

false data. This is especially true while writing to/reading from a bit

(or group of bits) among bits 16 - 31 */

struct ECAN_REGS ECanaShadow;

EALLOW; // EALLOW enables access to protected bits

/* Configure eCAN RX and TX pins for CAN operation using eCAN regs*/

ECanaShadow.CANTIOC.all = ECanaRegs.CANTIOC.all;

ECanaShadow.CANTIOC.bit.TXFUNC = 1;

ECanaRegs.CANTIOC.all = ECanaShadow.CANTIOC.all;

ECanaShadow.CANRIOC.all = ECanaRegs.CANRIOC.all;

ECanaShadow.CANRIOC.bit.RXFUNC = 1;

ECanaRegs.CANRIOC.all = ECanaShadow.CANRIOC.all;

/* Configure eCAN for SCC mode - (reqd to access mailboxes 0 to 15) */

ECanaShadow.CANMC.all = ECanaRegs.CANMC.all;

ECanaShadow.CANMC.bit.SCB = 0;

ECanaRegs.CANMC.all = ECanaShadow.CANMC.all;

/* Initialize all bits of 'Master Control Field' to zero */

// Some bits of MSGCTRL register come up in an unknown state. For proper operation,

// all bits (including reserved bits) of MSGCTRL must be initialized to zero

//ECanaMboxes.MBOX0.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX1.MSGCTRL.all = 0x00000000;

// ECanaMboxes.MBOX2.MSGCTRL.all = 0x00000000;

// ECanaMboxes.MBOX3.MSGCTRL.all = 0x00000000;

//ECanaMboxes.MBOX4.MSGCTRL.all = 0x00000000;

// ECanaMboxes.MBOX5.MSGCTRL.all = 0x00000000;

//ECanaMboxes.MBOX6.MSGCTRL.all = 0x00000000;

//ECanaMboxes.MBOX7.MSGCTRL.all = 0x00000000;

// ECanaMboxes.MBOX8.MSGCTRL.all = 0x00000000;

// ECanaMboxes.MBOX9.MSGCTRL.all = 0x00000000;

// ECanaMboxes.MBOX10.MSGCTRL.all = 0x00000000;

// ECanaMboxes.MBOX11.MSGCTRL.all = 0x00000000;

// ECanaMboxes.MBOX12.MSGCTRL.all = 0x00000000;

// ECanaMboxes.MBOX13.MSGCTRL.all = 0x00000000;

// ECanaMboxes.MBOX14.MSGCTRL.all = 0x00000000;

// ECanaMboxes.MBOX15.MSGCTRL.all = 0x00000000;

//ECanaMboxes.MBOX16.MSGCTRL.all = 0x00000000;

//ECanaMboxes.MBOX17.MSGCTRL.all = 0x00000000;

// ECanaMboxes.MBOX18.MSGCTRL.all = 0x00000000;

//ECanaMboxes.MBOX19.MSGCTRL.all = 0x00000000;

// ECanaMboxes.MBOX20.MSGCTRL.all = 0x00000000;

// ECanaMboxes.MBOX21.MSGCTRL.all = 0x00000000;

// ECanaMboxes.MBOX22.MSGCTRL.all = 0x00000000;

// ECanaMboxes.MBOX23.MSGCTRL.all = 0x00000000;

// ECanaMboxes.MBOX24.MSGCTRL.all = 0x00000000;

// ECanaMboxes.MBOX25.MSGCTRL.all = 0x00000000;

// ECanaMboxes.MBOX26.MSGCTRL.all = 0x00000000;

// ECanaMboxes.MBOX27.MSGCTRL.all = 0x00000000;

// ECanaMboxes.MBOX28.MSGCTRL.all = 0x00000000;

// ECanaMboxes.MBOX29.MSGCTRL.all = 0x00000000;

// ECanaMboxes.MBOX30.MSGCTRL.all = 0x00000000;

// ECanaMboxes.MBOX31.MSGCTRL.all = 0x00000000;

// TAn, RMPn, GIFn bits are all zero upon reset and are cleared again

// as a matter of precaution.

ECanaRegs.CANTA.bit.TA1 = 1 ; /* Clear all TA1 bits */

// ECanaRegs.CANRMP.bit.RMP1 = 1; /* Clear all RMPn bits */

ECanaRegs.CANGIF0.all = 0xFFFFFFFF; /* Clear all interrupt flag bits */

ECanaRegs.CANGIF1.all = 0xFFFFFFFF;

/* Configure bit timing parameters for eCANA*/

ECanaShadow.CANMC.all = ECanaRegs.CANMC.all;

ECanaShadow.CANMC.bit.CCR = 1 ; // Set CCR = 1

ECanaRegs.CANMC.all = ECanaShadow.CANMC.all;

ECanaShadow.CANES.all = ECanaRegs.CANES.all;

do

{

ECanaShadow.CANES.all = ECanaRegs.CANES.all;

} while(ECanaShadow.CANES.bit.CCE != 1 ); // Wait for CCE bit to be set..

ECanaShadow.CANBTC.all = 0;

#if (CPU_FRQ_150MHZ) // CPU_FRQ_150MHz is defined in DSP2833x_Examples.h

/* The following block for all 150 MHz SYSCLKOUT (75 MHz CAN clock) - default. Bit rate = 1 Mbps

See Note at End of File */

ECanaShadow.CANBTC.bit.BRPREG = 39;

ECanaShadow.CANBTC.bit.TSEG2REG = 2;

ECanaShadow.CANBTC.bit.TSEG1REG = 10;

#endif

#if (CPU_FRQ_100MHZ) // CPU_FRQ_100MHz is defined in DSP2833x_Examples.h

/* The following block is only for 100 MHz SYSCLKOUT (50 MHz CAN clock). Bit rate = 1 Mbps

See Note at End of File */

ECanaShadow.CANBTC.bit.BRPREG = 4;

ECanaShadow.CANBTC.bit.TSEG2REG = 1;

ECanaShadow.CANBTC.bit.TSEG1REG = 6;

#endif

ECanaShadow.CANBTC.bit.SAM = 1;

ECanaRegs.CANBTC.all = ECanaShadow.CANBTC.all;

ECanaShadow.CANMC.all = ECanaRegs.CANMC.all;

ECanaShadow.CANMC.bit.CCR = 0 ; // Set CCR = 0

ECanaRegs.CANMC.all = ECanaShadow.CANMC.all;

ECanaShadow.CANES.all = ECanaRegs.CANES.all;

do

{

ECanaShadow.CANES.all = ECanaRegs.CANES.all;

} while(ECanaShadow.CANES.bit.CCE != 0 ); // Wait for CCE bit to be cleared..

/* Disable all Mailboxes */

ECanaRegs.CANME.all = 0; // Required before writing the MSGIDs

EDIS;

}

#if (DSP28_ECANB)

void InitECanb(void) // Initialize eCAN-B module

{

/* Create a shadow register structure for the CAN control registers. This is

needed, since only 32-bit access is allowed to these registers. 16-bit access

to these registers could potentially corrupt the register contents or return

false data. This is especially true while writing to/reading from a bit

(or group of bits) among bits 16 - 31 */

struct ECAN_REGS ECanbShadow;

EALLOW; // EALLOW enables access to protected bits

/* Configure eCAN RX and TX pins for CAN operation using eCAN regs*/

ECanbShadow.CANTIOC.all = ECanbRegs.CANTIOC.all;

ECanbShadow.CANTIOC.bit.TXFUNC = 1;

ECanbRegs.CANTIOC.all = ECanbShadow.CANTIOC.all;

ECanbShadow.CANRIOC.all = ECanbRegs.CANRIOC.all;

ECanbShadow.CANRIOC.bit.RXFUNC = 1;

ECanbRegs.CANRIOC.all = ECanbShadow.CANRIOC.all;

/* Configure eCAN for HECC mode - (reqd to access mailboxes 16 thru 31) */

ECanbShadow.CANMC.all = ECanbRegs.CANMC.all;

ECanbShadow.CANMC.bit.SCB = 1;

ECanbRegs.CANMC.all = ECanbShadow.CANMC.all;

/* Initialize all bits of 'Master Control Field' to zero */

// Some bits of MSGCTRL register come up in an unknown state. For proper operation,

// all bits (including reserved bits) of MSGCTRL must be initialized to zero

ECanbMboxes.MBOX0.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX1.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX2.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX3.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX4.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX5.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX6.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX7.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX8.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX9.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX10.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX11.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX12.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX13.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX14.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX15.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX16.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX17.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX18.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX19.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX20.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX21.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX22.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX23.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX24.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX25.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX26.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX27.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX28.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX29.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX30.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX31.MSGCTRL.all = 0x00000000;

// TAn, RMPn, GIFn bits are all zero upon reset and are cleared again

// as a matter of precaution.

ECanbRegs.CANTA.all = 0xFFFFFFFF; /* Clear all TAn bits */

ECanbRegs.CANRMP.all = 0xFFFFFFFF; /* Clear all RMPn bits */

ECanbRegs.CANGIF0.all = 0xFFFFFFFF; /* Clear all interrupt flag bits */

ECanbRegs.CANGIF1.all = 0xFFFFFFFF;

/* Configure bit timing parameters for eCANB*/

ECanbShadow.CANMC.all = ECanbRegs.CANMC.all;

ECanbShadow.CANMC.bit.CCR = 1 ; // Set CCR = 1

ECanbRegs.CANMC.all = ECanbShadow.CANMC.all;

ECanbShadow.CANES.all = ECanbRegs.CANES.all;

do

{

ECanbShadow.CANES.all = ECanbRegs.CANES.all;

} while(ECanbShadow.CANES.bit.CCE != 1 ); // Wait for CCE bit to be cleared..

ECanbShadow.CANBTC.all = 0;

#if (CPU_FRQ_150MHZ) // CPU_FRQ_150MHz is defined in DSP2833x_Examples.h

/* The following block for all 150 MHz SYSCLKOUT (75 MHz CAN clock) - default. Bit rate = 1 Mbps

See Note at end of file */

ECanbShadow.CANBTC.bit.BRPREG = 4;

ECanbShadow.CANBTC.bit.TSEG2REG = 2;

ECanbShadow.CANBTC.bit.TSEG1REG = 10;

#endif

#if (CPU_FRQ_100MHZ) // CPU_FRQ_100MHz is defined in DSP2833x_Examples.h

/* The following block is only for 100 MHz SYSCLKOUT (50 MHz CAN clock). Bit rate = 1 Mbps

See Note at end of file */

ECanbShadow.CANBTC.bit.BRPREG = 4;

ECanbShadow.CANBTC.bit.TSEG2REG = 1;

ECanbShadow.CANBTC.bit.TSEG1REG = 6;

#endif

ECanbShadow.CANBTC.bit.SAM = 1;

ECanbRegs.CANBTC.all = ECanbShadow.CANBTC.all;

ECanbShadow.CANMC.all = ECanbRegs.CANMC.all;

ECanbShadow.CANMC.bit.CCR = 0 ; // Set CCR = 0

ECanbRegs.CANMC.all = ECanbShadow.CANMC.all;

ECanbShadow.CANES.all = ECanbRegs.CANES.all;

do

{

ECanbShadow.CANES.all = ECanbRegs.CANES.all;

} while(ECanbShadow.CANES.bit.CCE != 0 ); // Wait for CCE bit to be cleared..

/* Disable all Mailboxes */

ECanbRegs.CANME.all = 0; // Required before writing the MSGIDs

EDIS;

}

#endif // if DSP28_ECANB

//---------------------------------------------------------------------------

// Example: InitECanGpio:

//---------------------------------------------------------------------------

// This function initializes GPIO pins to function as eCAN pins

//

// Each GPIO pin can be configured as a GPIO pin or up to 3 different

// peripheral functional pins. By default all pins come up as GPIO

// inputs after reset.

//

// Caution:

// Only one GPIO pin should be enabled for CANTXA/B operation.

// Only one GPIO pin shoudl be enabled for CANRXA/B operation.

// Comment out other unwanted lines.

void InitECanGpio(void)

{

InitECanaGpio();

#if (DSP28_ECANB)

InitECanbGpio();

#endif // if DSP28_ECANB

}

void InitECanaGpio(void)

{

EALLOW;

/* Enable internal pull-up for the selected CAN pins */

// Pull-ups can be enabled or disabled by the user.

// This will enable the pullups for the specified pins.

// Comment out other unwanted lines.

//GpioCtrlRegs.GPAPUD.bit.GPIO30 = 0; // Enable pull-up for GPIO30 (CANRXA)

GpioCtrlRegs.GPAPUD.bit.GPIO18 = 0; // Enable pull-up for GPIO18 (CANRXA)

//GpioCtrlRegs.GPAPUD.bit.GPIO31 = 0; // Enable pull-up for GPIO31 (CANTXA)

GpioCtrlRegs.GPAPUD.bit.GPIO19 = 0; // Enable pull-up for GPIO19 (CANTXA)

/* Set qualification for selected CAN pins to asynch only */

// Inputs are synchronized to SYSCLKOUT by default.

// This will select asynch (no qualification) for the selected pins.

// GpioCtrlRegs.GPAQSEL2.bit.GPIO30 = 3; // Asynch qual for GPIO30 (CANRXA)

GpioCtrlRegs.GPAQSEL2.bit.GPIO18 = 3; // Asynch qual for GPIO18 (CANRXA)

/* Configure eCAN-A pins using GPIO regs*/

// This specifies which of the possible GPIO pins will be eCAN functional pins.

//GpioCtrlRegs.GPAMUX2.bit.GPIO30 = 1; // Configure GPIO30 for CANRXA operation

GpioCtrlRegs.GPAMUX2.bit.GPIO18 = 3; // Configure GPIO18 for CANRXA operation

// GpioCtrlRegs.GPAMUX2.bit.GPIO31 = 1; // Configure GPIO31 for CANTXA operation

GpioCtrlRegs.GPAMUX2.bit.GPIO19 = 3; // Configure GPIO19 for CANTXA operation

EDIS;

}

#if (DSP28_ECANB)

void InitECanbGpio(void)

{

EALLOW;

/* Enable internal pull-up for the selected CAN pins */

// Pull-ups can be enabled or disabled by the user.

// This will enable the pullups for the specified pins.

// Comment out other unwanted lines.

GpioCtrlRegs.GPAPUD.bit.GPIO8 = 0; // Enable pull-up for GPIO8 (CANTXB)

// GpioCtrlRegs.GPAPUD.bit.GPIO12 = 0; // Enable pull-up for GPIO12 (CANTXB)

// GpioCtrlRegs.GPAPUD.bit.GPIO16 = 0; // Enable pull-up for GPIO16 (CANTXB)

// GpioCtrlRegs.GPAPUD.bit.GPIO20 = 0; // Enable pull-up for GPIO20 (CANTXB)

GpioCtrlRegs.GPAPUD.bit.GPIO10 = 0; // Enable pull-up for GPIO10 (CANRXB)

// GpioCtrlRegs.GPAPUD.bit.GPIO13 = 0; // Enable pull-up for GPIO13 (CANRXB)

// GpioCtrlRegs.GPAPUD.bit.GPIO17 = 0; // Enable pull-up for GPIO17 (CANRXB)

// GpioCtrlRegs.GPAPUD.bit.GPIO21 = 0; // Enable pull-up for GPIO21 (CANRXB)

/* Set qualification for selected CAN pins to asynch only */

// Inputs are synchronized to SYSCLKOUT by default.

// This will select asynch (no qualification) for the selected pins.

// Comment out other unwanted lines.

GpioCtrlRegs.GPAQSEL1.bit.GPIO10 = 3; // Asynch qual for GPIO10 (CANRXB)

// GpioCtrlRegs.GPAQSEL1.bit.GPIO13 = 3; // Asynch qual for GPIO13 (CANRXB)

// GpioCtrlRegs.GPAQSEL2.bit.GPIO17 = 3; // Asynch qual for GPIO17 (CANRXB)

// GpioCtrlRegs.GPAQSEL2.bit.GPIO21 = 3; // Asynch qual for GPIO21 (CANRXB)

/* Configure eCAN-B pins using GPIO regs*/

// This specifies which of the possible GPIO pins will be eCAN functional pins.

GpioCtrlRegs.GPAMUX1.bit.GPIO8 = 2; // Configure GPIO8 for CANTXB operation

// GpioCtrlRegs.GPAMUX1.bit.GPIO12 = 2; // Configure GPIO12 for CANTXB operation

// GpioCtrlRegs.GPAMUX2.bit.GPIO16 = 2; // Configure GPIO16 for CANTXB operation

// GpioCtrlRegs.GPAMUX2.bit.GPIO20 = 3; // Configure GPIO20 for CANTXB operation

GpioCtrlRegs.GPAMUX1.bit.GPIO10 = 2; // Configure GPIO10 for CANRXB operation

// GpioCtrlRegs.GPAMUX1.bit.GPIO13 = 2; // Configure GPIO13 for CANRXB operation

// GpioCtrlRegs.GPAMUX2.bit.GPIO17 = 2; // Configure GPIO17 for CANRXB operation

// GpioCtrlRegs.GPAMUX2.bit.GPIO21 = 3; // Configure GPIO21 for CANRXB operation

EDIS;

}

#endif // if DSP28_ECANB

/*

Note: Bit timing parameters must be chosen based on the network parameters such

as the sampling point desired and the propagation delay of the network.

The propagation delay is a function of length of the cable, delay introduced by

the transceivers and opto/galvanic-isolators (if any).

The parameters used in this file must be changed taking into account the above

mentioned factors in order to arrive at the bit-timing parameters suitable

for a network.

*/

3. can rx

// TI File $Revision: /main/2 $

// Checkin $Date: July 30, 2009 18:44:22 $

//###########################################################################

// Filename: Example_28xEcan_A_to_B_Xmit.c

//

// Description: eCANA-1 to eCANA2 Transmit loop