Other Parts Discussed in Thread: C2000WARE

Hello everybody ,

please I m using a TMS device TMS320F28376DPTPT .

I m using all onboard comparators and only on some of them ( different comparator number on a different chip ) , I see a issue on DAC : there is about 300mV offset . So if I set DAC ref to zero , comparator will not change state unless I m over 300mV in input , and offset is there on all the input range ( so a 1V threshold for the comparators , I need an input of 1.3V ) .

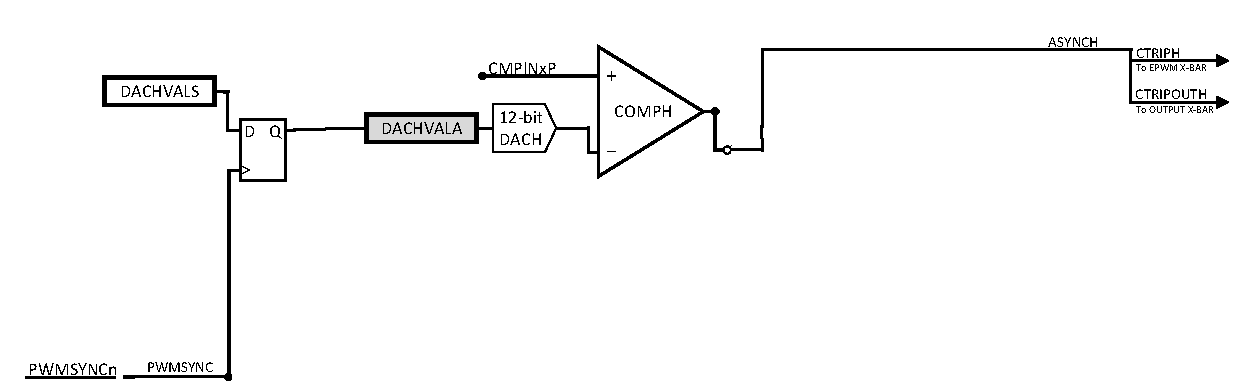

in attach the connection scheme I use .

I clear registrer DACHVALs , CPRIPH stays high ( comparator low ) till input of CMPINxP reaches 300mV . I checked same input voltage with internal ADC and I can see correctly the 300mV input so no issue in the board .

as said issue is there on different comparators ( some are working as I am expecting ) on different devices .

comparators ( some are working as I am expecting ) on different devices .

please where am I wrong ?

thank you

regards

Calro