Part Number: TMDSRSLVR

Hello,

I am developing some code for a resolver interface and I am porting the code for the resolver for a f28335 (controlSUITE\development_kits\TMDSRSLVR_v1.0\Resolver_f28335) to a TMS320F28379D.

I believe I understood most of the code, but there is one part that is very obscure to me:

the definition of the PWMs are as follows:

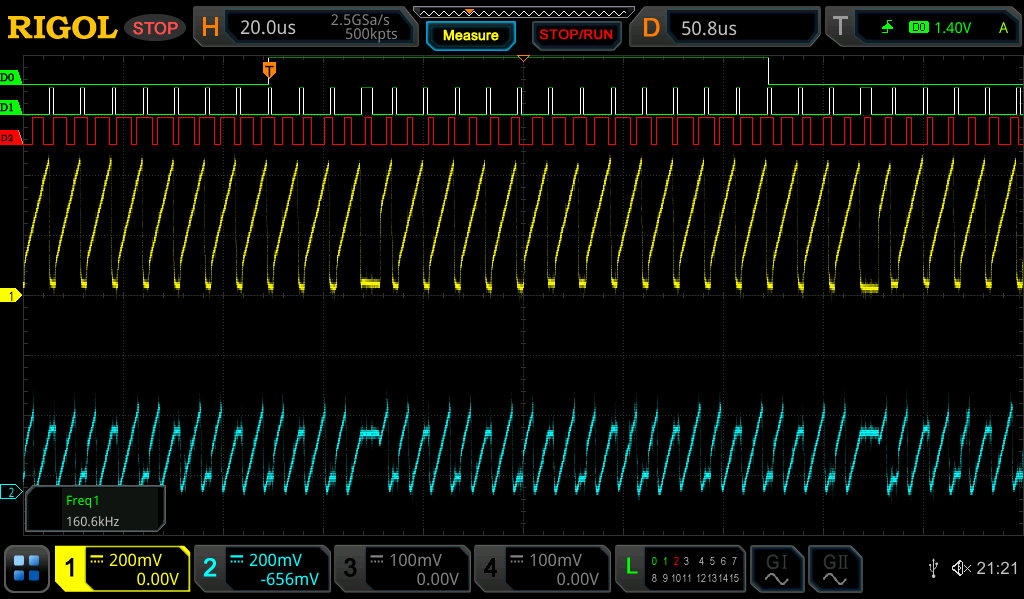

ePWM_1ch_CNF(&EPwm1Regs, TIMECNT_6p25uS, 1, 0); // 160KHz time base gen ePWM_1ch_CNF(&EPwm2Regs, SINE_CARRIER, 1, 0); // Sine carrier gen

Also "SINE_CARRIER" is defined as:

#define SINE_CARRIER (250*2.5) /* 2.5 for Delfino, 1 for Piccolo */

Now, the initialization for EPwm1 is clear that needs to have a frequency of 160kHz, however I don't undestand the 250 (or 625 for piccolo).

If the sinewave is to be updated every 6.25us (160kHz), shouldn't its carrier also have the same period?

What are these 250 and 625 numbers based on?

Thanks