Other Parts Discussed in Thread: C2000WARE

Hi

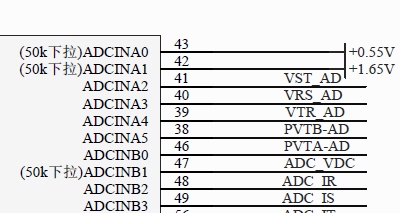

My customer use TMS320F28075 ADC to sample three-phase electric power.

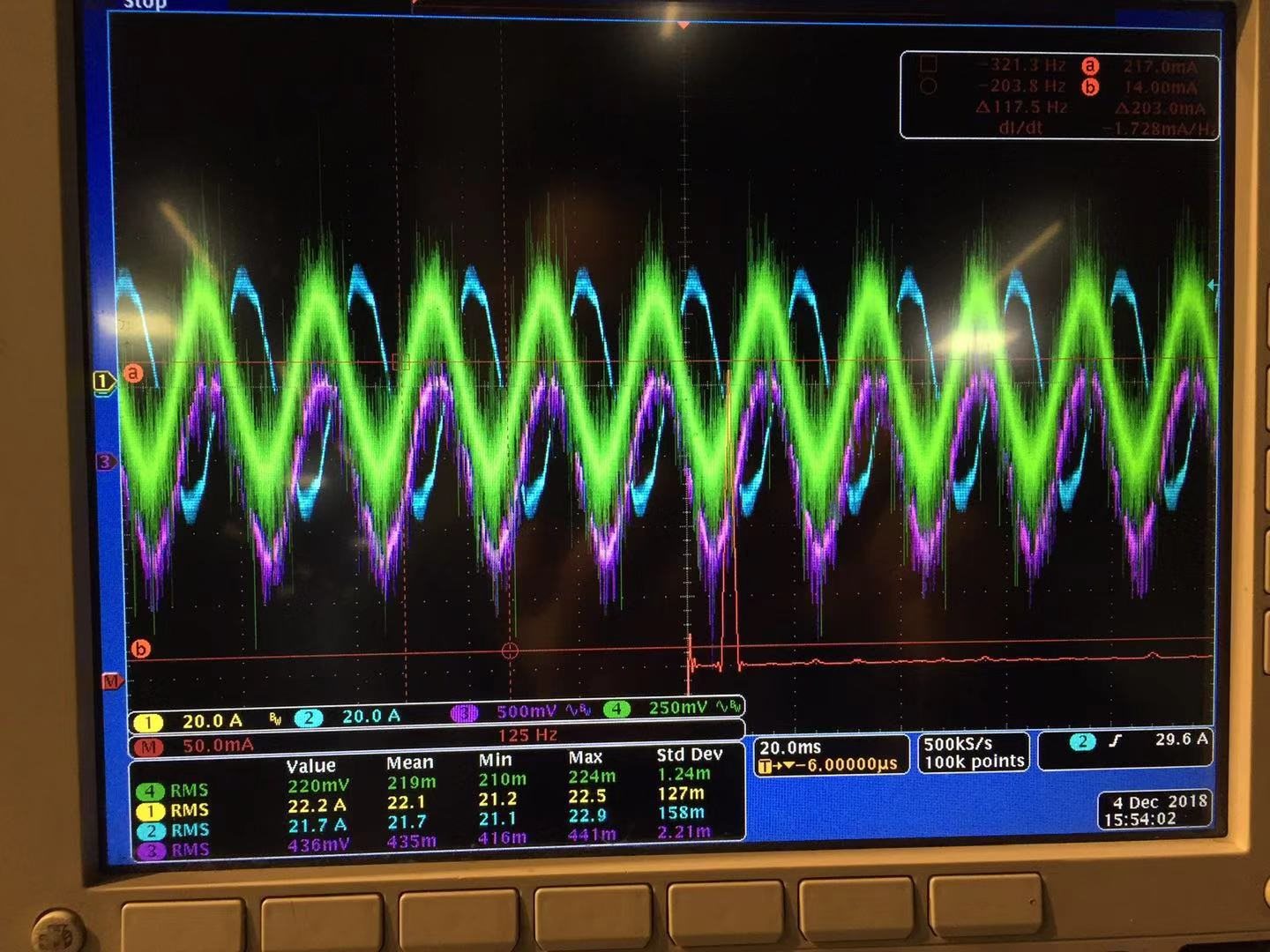

As you see, the green wave is voltage input to ADC. Fundamental is 50Hz, almost hasn't 100Hz harmonic.

The purple is the converted wave from digital ADC sampling result. 100Hz harmonic become heavy.

Analog input hasn't 100Hz 2nd harmonic, why the ADC sampling result has so heavy 2nd harmonic? Thanks.