Other Parts Discussed in Thread: OPA4170

Hi,

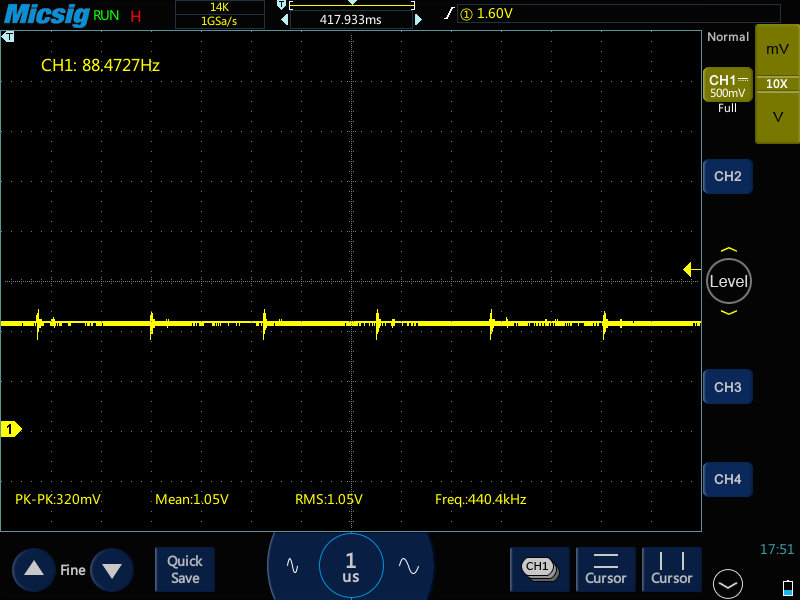

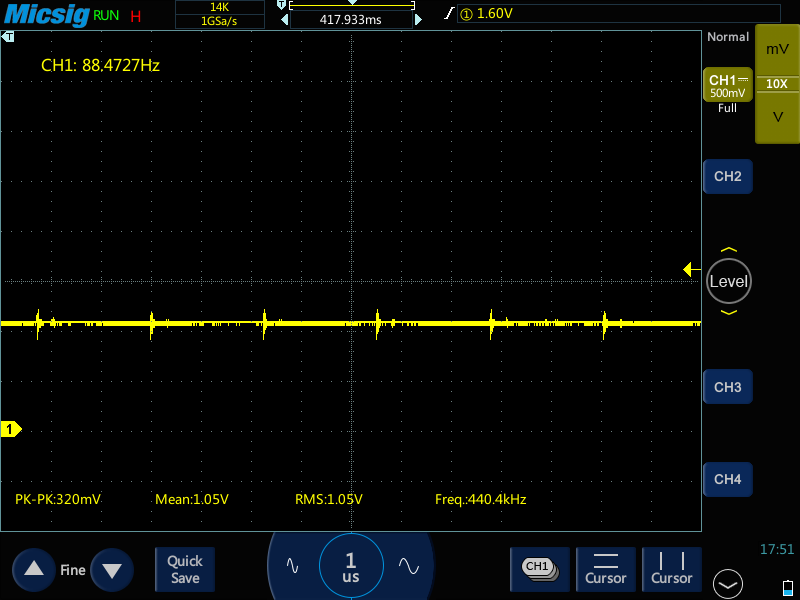

I have arranged parallel 100pF or 22pF capacitor on the input side of ADC. Which generate oscillate input for ADC.

I request you so kindly provide us your valuable suggestion to unwanted oscillated input for ADC. so we can move forward our design

Below image for your reference

Regards,

Chirag Rana