I am having issues with the output of EPWM1 of the F28027 control card set up to toggle the output, as follows:

EPwm1Regs.AQCTLA.bit.ZRO = 0x3; // when counter = zero toggles EPWM1A output

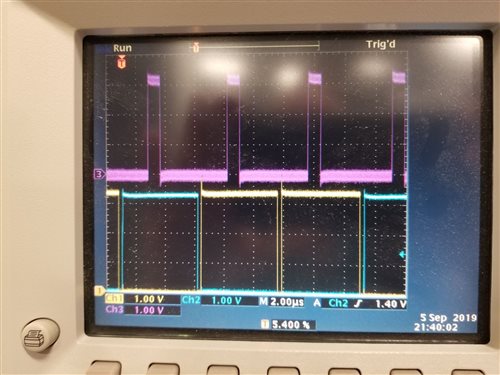

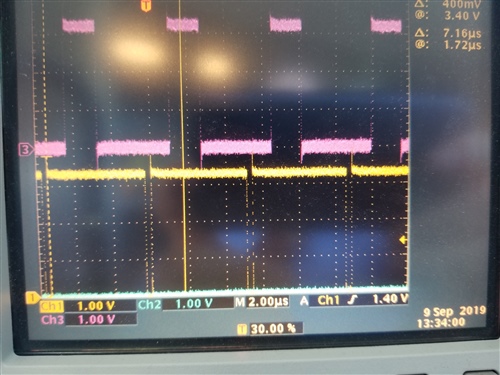

The problem is shown below. The yellow trace is EPWM1A and the blue is EPWM1B. Two consecutive pulses of EPWM1A are captures in this single-shot trace. (The pink trace is EPWM4, used to generate ISR and ramp start timings).

I have EPWM1 set up so a comparator can generate a sync event that loads the TBPHS value (=0) into the time base register. If the comparator doesn't trip then EPWM1 resets at the value MAX_PERIOD. The double pulsing occurs when the comparator trips just before MAX_PERIOD, so that the comparator sync is coincident or almost coincident with MAX_PERIOD. The waveforms shown here are being generated with DC voltages to the comparator inputs, and there is no switching electronics being controlled by the EPWM outputs.

Is there any way to suppress this double pulsing? This behavior would be disastrous if I actually had the switching electronics hooked up to the controller.

Here is the relevant code:

EALLOW;

// Configure ePWM1AB (used to switch primary half-bridge FETs)

PWM_ComplPairDB_CNF(1, MAX_PERIOD, 1, 0); // configures EPWM1 with complementary outputs, 1=master mode, 0=phase

EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO; // sync output when counter = 0

EPwm1Regs.TBCTL.bit.PHSEN = 1; // enable loading counter register from phase register

EPwm1Regs.TBPHS.half.TBPHS = 0; // phase register value

EPwm1Regs.TBCTL.bit.PHSEN = 0x1; //Causes counter to become TBPHS at sync

EPwm1Regs.TBPHS.half.TBPHS = 0x0; // Set counter to 0 at sync

EPwm1Regs.DCTRIPSEL.bit.DCAHCOMPSEL = DC_COMP1OUT; // 8 = DCAH = Comparator 1 output initially (alternates between Comp1 and Comp2 each phase)

EPwm1Regs.TZDCSEL.bit.DCAEVT1 = TZ_DCAH_HI; // 2 = DCAEVT1 set on DCAH high(will become active as Comparator output goes high)

EPwm1Regs.DCACTL.bit.EVT1SRCSEL = 1; // 1 = Source Is DCEVTFILT Signal (filtered by event window, see below)

// EPwm1Regs.DCACTL.bit.EVT1FRCSYNCSEL = 0; // 0 = SYNC path for DCAEVT1.force

EPwm1Regs.DCACTL.bit.EVT1SYNCE = 0x1; // 1 = SYNC Generation Enabled

EPwm1Regs.TZCTL.bit.DCAEVT1 = 0x3; // Do nothing on EPWM1A output on event

EPwm1Regs.DCFCTL.bit.SRCSEL = DC_SRC_DCAEVT1; // 0 = Filter source = DCAEVT1

EPwm1Regs.DCFCTL.bit.PULSESEL = DC_PULSESEL_ZERO; // 1 = Filter start on TBCTR = ZERO

EPwm1Regs.DCFCTL.bit.BLANKE = DC_BLANK_ENABLE; // 1= Enable Blanking window

EPwm1Regs.DCFCTL.bit.BLANKINV = 0; // 0 = Blanking window not inverted

EPwm1Regs.DCFOFFSET = 0; // Filter offset

EPwm1Regs.DCFWINDOW = MIN_PERIOD; // blanking ends just after ramp is triggered

EPwm1Regs.AQCTLA.bit.ZRO = 0x3; // when counter = zero toggles EPWM1A output

EPwm1Regs.AQCTLA.bit.CAU = 0x0; // Do nothing (action disabled)

EPwm1Regs.AQCTLA.bit.PRD = 0x0; // Do nothing (action disabled)

PWM_ComplPairDB_UpdateDB(1, RED, FED); // sets the deadband timing

// Configure PWM2A

PWM_1ch_UpCntDB_Compl_CNF(2, MAX_PERIOD, 0, 0); // changed period to MAX_PERIOD

PWM_1ch_UpCntDB_Compl_UpdateDB(2, REM1, FEM1);

// Configure PWM3A

PWM_1ch_UpCntDB_CNF(3, MAX_PERIOD, 0, 0); // changed period to MAX_PERIOD

PWM_1ch_UpCntDB_UpdateDB(3, REM2, FEM2);

// Configure EPWM4

PWM_1ch_CNF(4, MAX_PERIOD, 0, MIN_PERIOD+MIN_DELTA); // changed to slave and period to MAX_PERIOD

// EPwm4Regs.CMPCTL.bit.SHDWAMODE = 1; // Immediate mode. Only the active compare A register is used.

EPwm4Regs.CMPA.half.CMPA = MAX_PERIOD-50; // Sets EPWM4 output pulse start and trigger point for CNTL_ISR

EPwm4Regs.AQCTLA.bit.ZRO = 0x1; // output low

EPwm4Regs.AQCTLA.bit.CAU = 0x2; // output high

EPwm4Regs.AQCTLA.bit.PRD = 0x0; //Do nothing (action disabled)

// Configure the comparator and ramp generator block

DacDrvCnf(1, 0x7FFF, 1, 4, Slope); //ADDED FOR PQMC: Comp1, DACVAL=max Q15, DACSOURCE=rampgen=1, RAMPSOURCE=PWM4

Comp1Regs.COMPCTL.bit.SYNCSEL = 0; // don't filter the comparator output

DacDrvCnf(2, 0x7FFF, 1, 4, Slope); //ADDED FOR PQMC: Comp2, DACVAL=max Q15, DACSOURCE=rampgen=1, RAMPSOURCE=PWM4

Comp2Regs.COMPCTL.bit.SYNCSEL = 0; // don't filter the comparator output

EDIS;

Thanks for the help,

Ciaran