Part Number: TMS320F28377S

Other Parts Discussed in Thread: UNIFLASH, C2000WARE

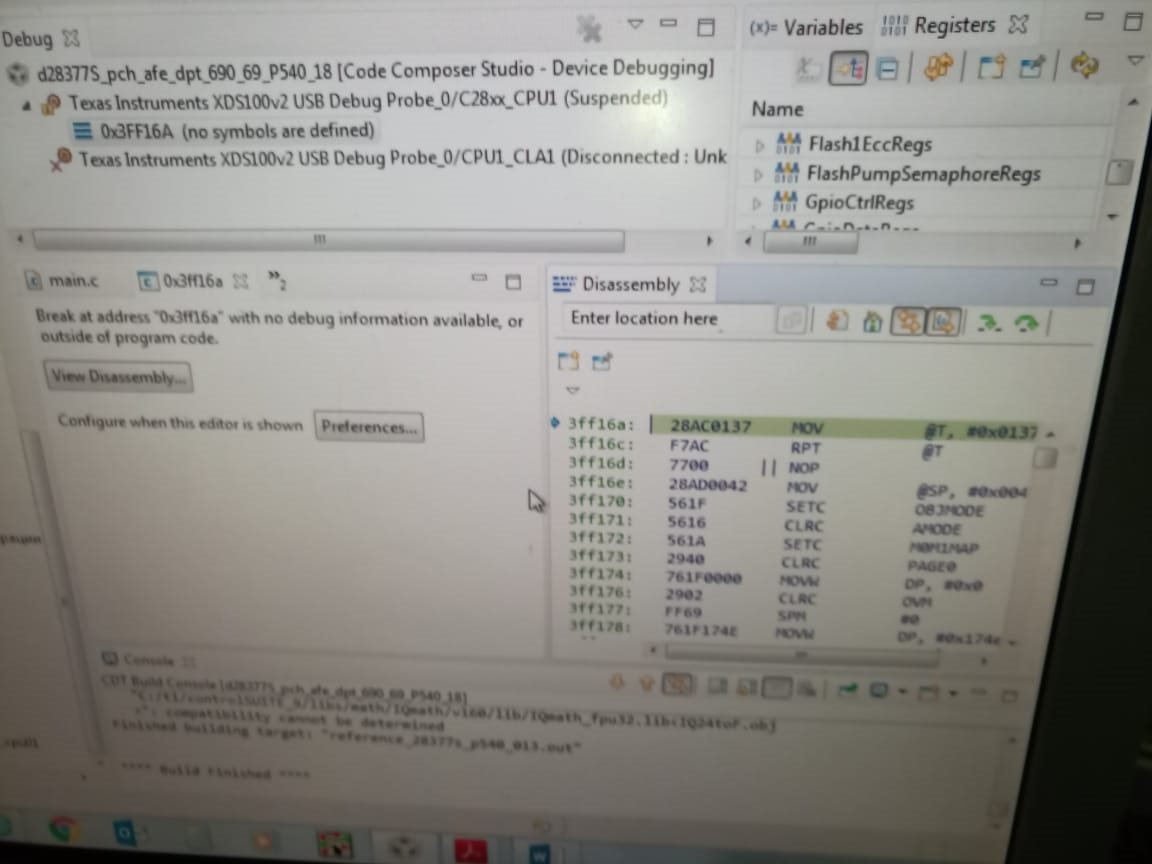

Tool/software: Code Composer Studio

Hello. I am learning the programming of TMS320f28377S and faced a problem - after programming the controller and resetting the power supply, it does not start. When debugging (JTAG) everything is fine. The GPIO84 and GPIO 72 ports are powered up. The recording goes to flash. We used free sample for experiments . Maybe it can't load from flash?