Part Number: TMS320F280049

Other Parts Discussed in Thread: C2000WARE

Dear champs,

I am asking this for our customer.

The user uses TI example "hrpwm_ex2_prdupdown_sfo_v8" with only modifying following line 286 and line 287 to set PWM1A and PWM1B in complementary.

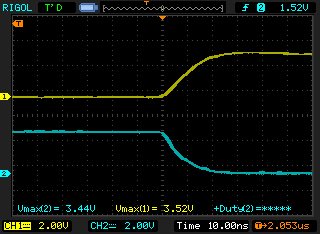

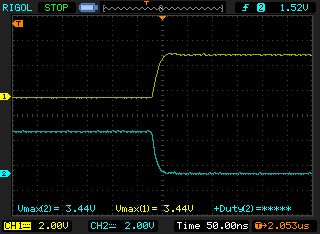

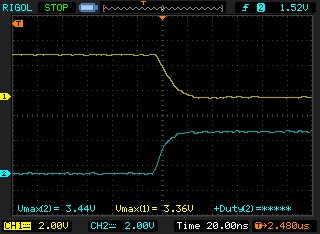

On the oscilloscope snapshot below, the duty time of PWM 1A differs from the duty time of PWM 1B by about 17.6 ns. It appears the duty of yellow is larger than that of blue, which is not desired.

Questions:

1. In theory, the duty should be 50% in PWM1A and PWM1B. Why the difference time of PWM1A duty and PWM 1B duty is so large up to 10 to 20 ns, especially they are in HRPWM? The user desires the difference should be around 150 ps.

2. The user's goal is to have PWM 1A and 1B in complementary with 50% duty with fixed or changing periods. And the duty difference of PWM1A and PWM1B should be around 150 ps. What should the user do?

Wayne Huang