Hi expert,

I am supporting customer configuring F280048 project.

And they use an 16MHz XTAL_OSC

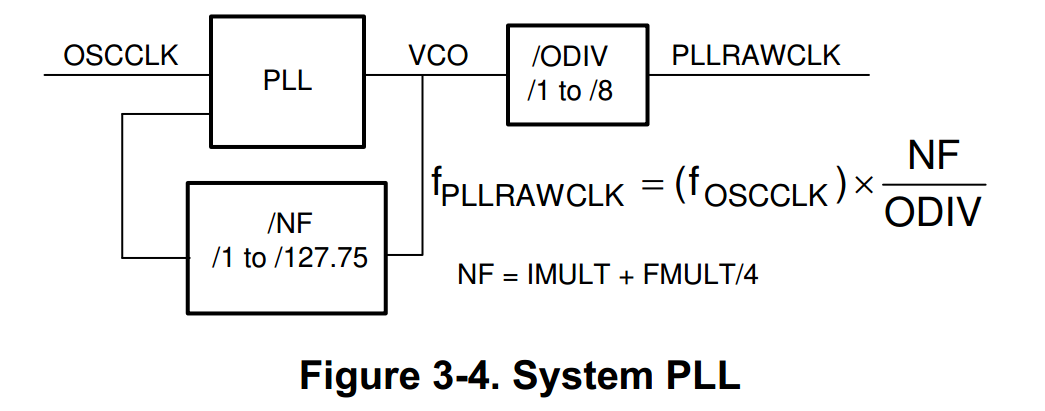

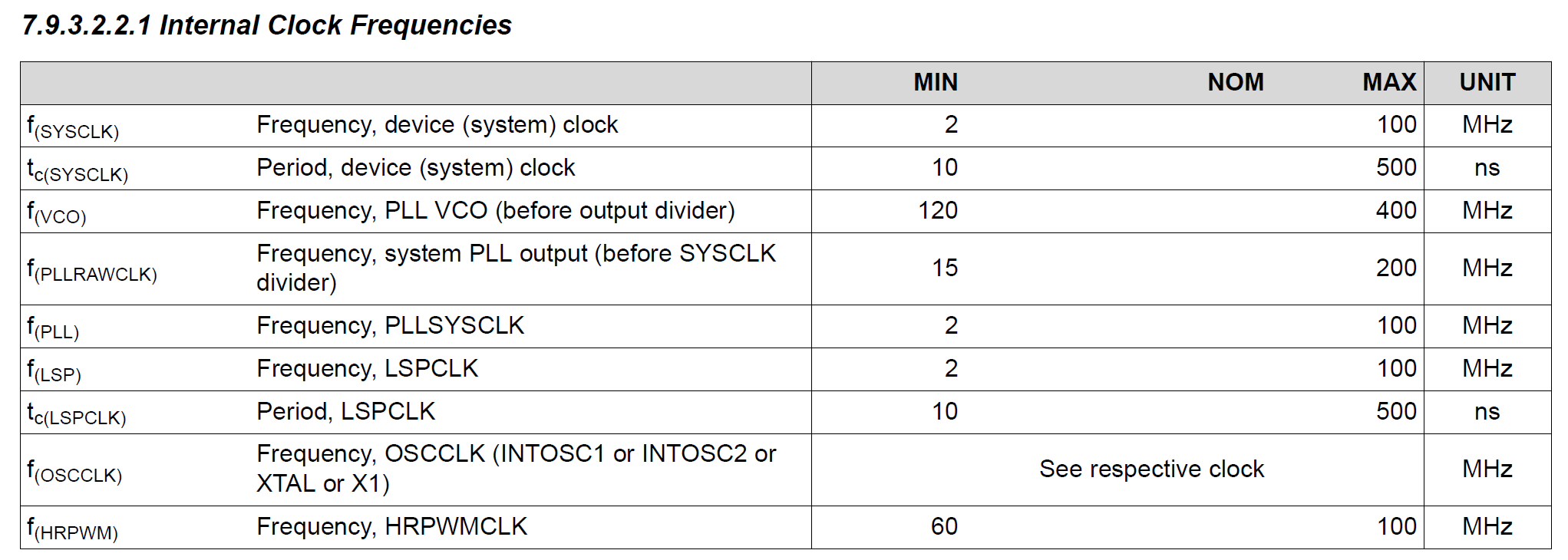

according to the datasheet, PLL structure.

I think there are two method to achieve it.

one is

// PLLSYSCLK = 16MHz (XTAL_OSC) * 25 (IMULT) * 1 (FMULT) / 4 (PLLCLK_BY_4)

SysCtl_setClock(SYSCTL_OSCSRC_XTAL |

SYSCTL_IMULT(25) |

SYSCTL_FMULT_NONE |

SYSCTL_SYSDIV(4) |

SYSCTL_PLL_ENABLE);

the other is

// PLLSYSCLK = 16MHz (XTAL_OSC) * 12 (IMULT) * 0.5 (FMULT) / 2 (PLLCLK_BY_2)

SysCtl_setClock(SYSCTL_OSCSRC_XTAL |

SYSCTL_IMULT(12) |

SYSCTL_FMULT_1_2 |

SYSCTL_SYSDIV(2) |

SYSCTL_PLL_ENABLE);

and I found they both meet the clock spec,

did you find any mistake?

which one do you recommend?

BR

Emma