Dear Expert,

Pls help check my falure case, Thank you.

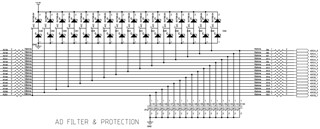

AD problem of DSP

TMS320F28335PGFA

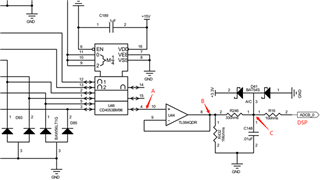

Fault phenomenon: running for a period of time, the signal appears abnormal: The basic circuit is as follows:

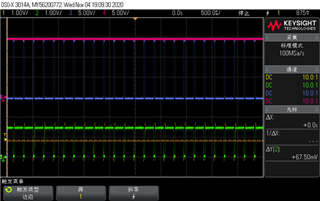

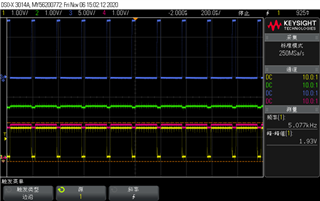

Under normal circumstances, the waveforms of A, B and C are the same, as below:

Yellow and Green are the waveforms for point A and C, Blue is the gating control signal from Analog switch CD4053, and Red is the +15V power supply. The expansion diagram as below:

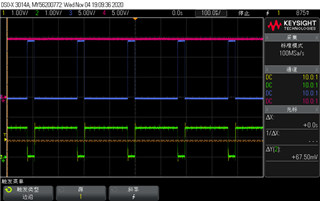

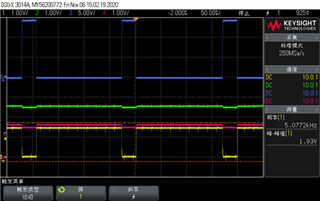

Waveform when failure: Yellow is point A, Red is point B, Green is point C, Blue is analog switch CD4053 gate control:

It seems that the output of the op-amp is pulled up from +1.5V to 1.7V and 0V to 1.5V. After R246, point C is pulled up to the voltage between 2.5V and 2.6V, as below:

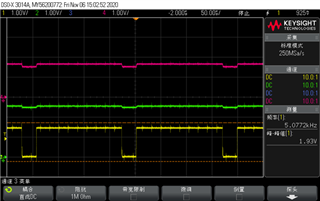

When failure, disconnected signals of R16, then signals of Point A, B and C were all restored to normal status, and the ADCB_0 signal sent to DSP was changed to +3.3V.

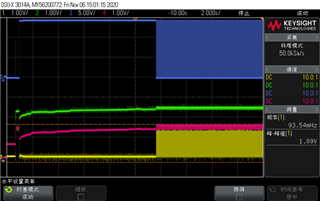

Failure startup waveform: Yellow is point A, Green is point C, Blue is analog switch selection signal, Red is point B.

Normal startup waveform: Yellow is point A, Green is point C, Blue is analog switch selection signal, Red is point B. Red is +15V power supply.